2.2.2.1 SPI Schnittstelle

DasSerial Peripheral Interface, abgekürzt SPI,

wurde im Jahr 1987 von der Firma Motorola entwickelt und verfügt über

drei Leitungen für eine serielle synchrone Datenübertragung zwischen

verschieden ICs.

(Serial Peripheral Interface - Mikrocontroller.net, 2019)

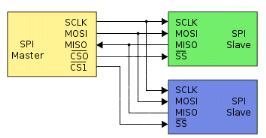

Es handelt sich um ein Master-Slave-Zugriffsverfahren,was

bedeutet, dass es einen Master, also Befehlenden, gibt (hier den Raspberry Pi),

der zyklisch die Verbindung mit anderen Teilnehmern bzw. Slave, also

Ausführenden,erstellt. Diesgeschieht mit Hilfe einer weiteren

CS - Leitung (Chip Select),die dazu dient, einzelne Teilnehmer zu

adressieren. Durch MOSI- und

MISO-Datenleitungen können Daten in beide Richtungen

gleichzeitig übertragen werden. Die Kommunikation erfolgt in Vollduplex

oder imGegenbetrieb. Der direkte Nachrichtaustausch zwischen einzelnen Slaven

ist nicht möglich. Das folgende Diagramm zeigt eine SPI-Bus-Kommunikation

mit zwei Slaves. Der Slave kann ein beliebiges Bauteil mit SPI Schnittstelle

sein.

(Kofler, Kühnast, & Scherbeck, 2018)

Abbildung 6: SPI-Bus mit einem

Master und zwei Slaven(Hochschule München, FK 04, Prof. Jürgen Plate,

2017).

SCLK: Serial Clock

MOSI: Master Out Slave In

MISO: Master In Slave Out

CS/SS: Chip Select/Slave Select

2.2.2.2 MCP-2515

1

2

13

12

3

5

11

8

9

10

4c

6

7

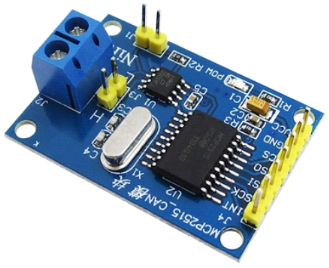

Abbildung7: Der MCP2515

CAN-Controller mit TJA1050 CAN-Transceiver(42project, 2019).

1:INT (Interrupt)

2: SCK (Serial Clock)

3: MOSI (Master Output Slave Input) SPI-Schnittstelle

4: MISO (Master Input slave Output)

5: CS (Chip Select)

6: GND (Ground)

7: VCC

8:MCP2515 Controller

9: TJA1050 CAN Transceiver

10: 8MHz Crystal

11: Jumper für120 Ohm Abschlusswiderstand

12: CAN High

13: CAN Low

Der MCP2515 (mit TJA1050 Transceiver)ist ein CAN-Bus-Modulmit

SPI-Schnittstellen. Dieser Baustein besteht aus einem CAN Controller(MCP2515)

und einemTransceiver (TJA 1050). Die Aufgabe der CAN Controllerbesteht

darin,das CAN-Protokoll zu implementieren, indem er dafür sorgt, dass

Daten rechtzeitig gesendet bzw. empfangen werden.Daten können mit einer

Bitrate von biszu1Mbits/s übertragen werden. DerTransceiver dagegen

wandelt das Signal von Steuergerät (Hier der Raspberry Pi) in die

Datenbusleitungen und empfängt die Daten von Slaven und wandelt sie

für den CAN-Controller um.(Wiesinger, 2018)

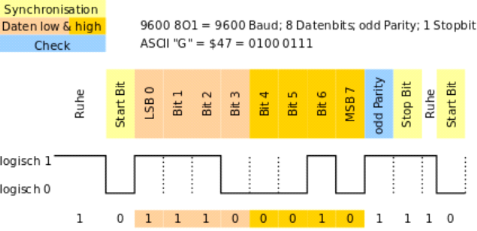

2.2.3 UART-Bus

Die UART-Schnittstelle bietet eine serielle asynchrone

Datenübertragung. Asynchron bedeutet, dass es kein-Tack Signal für

das Senden bzw. den Empfang einer Nachricht gibt. Dieses Bussystem dient zur

Kommunikation mit der RS232- und Rs485-Schnittstelle und benutzt für die

Kommunikation zwei Leitungen TxD (Transceiver Data) und RXD (Receiver Data).Die

UART-Schnittstelle istaktuell wegen ihres einfachen Aufbausund

ihrerZuverlässigkeitder Standard serieller Schnittstellen an PCs und

Mikrocontrollers.Damit der Datenaustausch erfolgreich funktioniert, ist es

erforderlich, dass Sender und Empfänger die gleiche

Übertragungsgeschwindigkeit (Baudrate)aufweisen.Der Aufbau einer Nachricht

mit der UART-Schnittstelle besteht aus bis zu 11 Bits. Die Nachricht beginnt

mit einem Startbit (dieser wird mit 0, Dominat Bit,gekennzeichnet), danach

folgen fünf bis max. acht Datenbits und sie endet mit einem Stoppbit, das

immer eine logische Eins erhält. Diese Start- und Stoppbits am Anfang und

Ende der Nachricht bilden dasKennzeichen für die Synchronisation

derDatenübertragung bei dem Universal Asynchronous Receiver

Transceiver.Damit Fehler erkannt werden, kann nach den Datenbits ein

Parität-bit gesendet werden(Schnell & Wiedemann, 2018).

Die folgende Abbildung zeigt einenausführlichen Aufbau

eines UART Frame.

Abbildung 8: UART Frame

(buyzero, 2019)

|