2.2 Architecture des FPGAs

2.2.1 Introduction

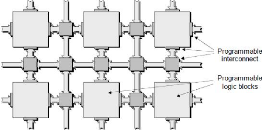

C'est une famille de puces électroniques introduite par

la société Xilinx. Les FPGAs sont les premières

architectures reconfigurables à avoir été

proposées. Ils ont l'avantage d'être recongurables à

souhait. Ils comprennent des blocs configurables qui permettent de

générer des fonctions logiques combinatoires ou

séquentielles sur 1 bit. Ainsi, en associant plusieurs

éléments configurables de 1 bit par le biais d'interconnexions

tout aussi programmables (Figure 4), l'utilisateur est capable de

générer n'importe quelle fonction logique.

Si le nombre d'unités configurables est suffisamment

important, il est possible, en associant ces blocs, de recréer un

système entier. C'est pour cette raison que ces composants sont

utilisés pour faire des prototypes de circuits, avant de les envoyer

chez le fondeur de silicium. Son développement s'est

accéléré sous la double pression du

«Time-To-Market»1 et de

«FirstTime-Right»2 (minimiser d'une part le temps

de développement et de mise sur le marche des circuits digitaux et

d'autre part éviter toute défaillance dans leur conception).

2.2.2 Principe de fonctionnement et Architecture Interne

des FPGAs

La structure interne ainsi que la technologie utilisées

dans les FPGAs varient suivant les fabricants. Mais la structure globale de la

Figure 4 (si on y rajoute les entrées/sorties programmables)

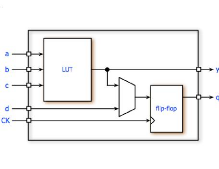

est valable indépendamment des fabricants. En général le

bloc configurable est bati autour d'un LUT (Look-Up-Table, voir Figure

5). Un LUT permet d'implémenter toute fonction combinatoire (ou

séquentielle, d'où le flip-flop de sortie) à quatre

entrées.

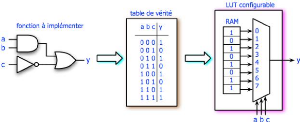

La Figure 6 présente l'implémentation

d'une fonction combinatoire a l'aide d'une LUT. La table de vérite de la

fonction est stockée dans une RAM connectée à un

multiplexeur. Configurer une LUT revient donc à stocker la table de

vérite de la fonction dans sa RAM et à router les signaux a, b et

c vers les entrées de sélection du multiplexeur.

1 Le Time-To-Market qui traduit donne «temps de mise

sur le marché» est vrai challenge pour reduire le temps de

developpement d'un nouveau produit électronique afin de s'adapter a la

reduction croissante du cycle de vie de produits électroniques grands

publics.

2 Le First-Time-Right par contre traduit la

nécessité d'éviter toute erreur dans la conception d'un

circuit avant l'envoi chez le fondeur d'ASIC; en effet un ASIC

défectueux coute en NRE (Non Recurring Engineering), cette somme que les

fournisseurs d'ASIC facturent au concepteur des le démarrage de

processus de fabrication. Dans tous les cas, le cout de la technologie ASIC

contribue largement a l'émergence des FPGAs.

Figure 4 : Structure globale des FPGAs [14]

Figure 5 :

Un LUT (Look-Up-Table) [14]

Figure 6: Implémentation d'une fonction Y = ab +

(non)C [14]

Grâce à sa granularité fine, on est

capable avec un circuit FPGA d'exploiter le parallélisme autant qu'avec

un circuit spécifique ASIC dans la mesure où l'on est capable de

le recréer entièrement par association des éléments

configurables. Mais cette fine granularité qui offre toute la

flexibilité logique voulue est au prix d'une performance moindre

comparée aux ASICs. En effet, elle apporte deux problèmes :

- La baisse de la fréquence de fonctionnement due au temps

de propagation des signaux.

- L'augmentation des temps de reconfiguration requis, ce qui

peut empêcher par exemple d'enchaîner sur le même circuit

deux configurations pour des applications à contraintes temps

réel [2].

Grâce aux avancées technologiques, les FPGAs sont

envisagés aujourd'hui (sur les plans du coût et des performances)

comme une alternative entre les solutions dédiées très

performantes (ASIC) et les solutions programmables très flexibles

(processeurs et DSP). Les principaux fabricants proposent aujourd'hui des FPGAs

intégrant jusqu'à 10 millions de portes logiques, et sur lesquels

on peut même synthétiser un coeur de microprocesseur (Microblaze

sur FPGAs Xilinx [21], Nios sur ceux d'Altera). De même, les FPGAs

à mémoire de configuration de type SRAM1 permettent la

reconfiguration dynamique. C'est le cas du Virtex-II Pro.

|