2.1 Implémentation logicielle vs

implémentation matérielle d'une application

2.1.1 Implémentation logicielle (Figure 3.a)

Dans un modèle d'exécution logicielle, le

traitement est séquentiel et exécuté par un processeur. En

effet, un CPU (Central Processing Unit) exécute une tâche (ou une

operation) à la fois. Toute application est découpée en

tâches unitaires exécutées les unes à la suite de

autres (Figure 3.a). Le passage d'une tâche à l'autre

nécessite une sauvegarde de contexte (context switch) qui permet de

conserver la cohérence globale de l'application, et donner une apparence

d'exécution parallèle des tâches. Mais ce modèle

nécessite des processeurs de plus en plus rapides pour répondre

à la complexité algorithmique des applications. Or les

fréquences de fonctionnement des processeurs ne sauraient être

augmentées indéfiniment a cause d'une part des limites

technologiques, et d'autre part d'une augmentation de la consommation qui n'est

pas souhaitable dans les systèmes embarqués.

Figure 3 : Implémentation temporelle vs

implémentation spatiale [13]

2.1.2 Implémentation matérielle (Figure

3.b)

Par contre dans un ASIC ou un FPGA, les applications

(algorithmes, fonctions, etc...) décrites dans un langage de description

de circuits (VHDL, Verilog, etc...) sont implémentées

matériellement; ceci apporte un gain de performance supérieur

à celui des processeurs grâce à l'implémentation

spatiale (parallèlisme) des tâches [13]. En effet dans ce type

d'implémentation matérielle, seul le temps de propagation des

signaux de l'entrée à la sortie d'un système fixe sa

limite supérieure en fréquence.

En outre, la reconfigurabilité dynamique de

certains FPGAs permet de faire évoluer l'architecture pour s'adapter au

traitement (Figure 3.c), contrairement aux ASICs. Il est aujourd'hui

envisagéable d'implémenter et d'exécuter

séquentiellement sur ce type de composants reconfigurables plusieurs

algorithmes, et de profiter à la fois de leur reconfigurabilité

(flexibilité) et de leur performance. Pour cela une architecture

reconfigurable inclut généralement deux principales parties, une

partie matérielle et une partie logicielle. La partie logicielle

comprend généralement un processeur (à usage

générique - GPP ou orienté traitement du signal -

DSP) chargé du contrôle et de la gestion de la

reconfiguration de la partie

matérielle, ainsi que de l'exécution des

tâches encore dévolues au logiciel. Elle utilise la partie

matérielle (un ou plusieurs FPGAs) comme accélérateur

matériel, en y implémentant les parties les plus critiques des

traitements.

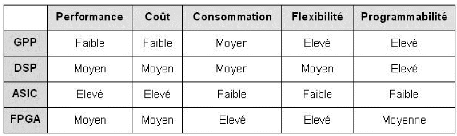

Le tableau comparatif ci-dessous (Table 1) permet de

situer les FPGAs parmi les principaux types d'architectures et leurs

caractéristiques [6].

Table 1 : Comparatif des caractéristiques de

différentes implémentations [6]

|