ANNEXE 3: UTILISATION DE LA PLATE-FORME DE

DEMONSTRATION

3.1 Génération des bitstreams a partir des

du répertoire Modular

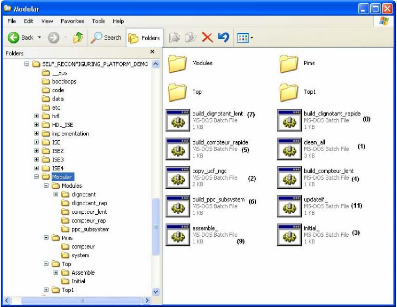

La fenêtre ci-dessous montre le contenu du

répertoire Modular qui contient tous les sous

répertoires et les fichiers permettant de dérouler les

étapes du Modular Design Flow. Nous supposons que :

- Le module « system a processeur » a été

teste et validé sous EDK puis exporte vers ISE.

- La synthèse des designs du module reconfigurable a

été réalisée et validée dans des projets

ISE, et associés aux divers projets du top.

- La synthèse d'au moins un Top a été

réalisée et le fichier top.ngc se trouvant dans le

répertoire

ISE correspondant.

- Le fichier de contrainte top.ucf a été

édité et se trouve dans le répertoire ISE.

- L'exécutable (fichier.elf) a été

correctement testé et validé dans un flot intégré

(Xflox) sous EDK

(avant exportation).

- L'HyperTerminal a été parametré suivant la

Figure Annexe 5.

Figure Annexe 4 : Le repertoire Modular avec les fichiers de

commande pour le Modular Design

Les fichiers Batch du répertoire permettent de

dérouler le Modular Design Flot de l'Initial Budgetting à la

Phase finale d'assemblage (voir phases 1 a 11 Figure Annexe 4).

Suivre simplement les étapes de (1) a (9) pour

générer les bitstreams partiels de tous les designs. Les

étapes (4), (5), (7) et (8) ne seront réalisées que si les

designs y afférents ont été effectivement

synthétises).

Apres la phase d'assemblage (9), la phase (10)

consistera a éditer le fichier system.bmm

comme montre en annexe 2. Ce fichier doit être ensuite recopie dans le

répertoire Top/Assemble.

La phase (11) consiste a produire a partir de

trois fichiers (.bit, .elf et .bmm) un fichier unique prêt a configurer

totalement le FPGA.

Apres cette configuration totale, le processeur lance

l'application que nous avons écrite, et affiche via l'HyperTerminal

l'invite de la figure Annexe 6.

Dans cet exemple, le module fixe (ppc_subsystem) est

assemblé dans Top/Assemble avec le dernier design de module

reconfigurable a avoir écrit dans le répertoire Pims (avec la

commande Pimcreate lors de la phase active d'implémentation).

Les fichiers .batch sont en Annexe 4.

3.2 Paramètres de configuration de

l'HyperTerminal

La Vitesse de transmission (19600 bits/sec) est celle qui a

été choisie lors de l'implémentation de l'UART. Pour

accélérer le transfert des fichiers de configuration

Figure Annexe 5 : Paramètres de configuration de

l'HyperTerminal.

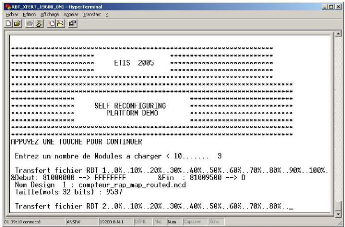

3.3 Message d'accueil de la demo

Pour envoyer un bitstream partiel en format .rbt, cliquer sur

transfert et choisir le format texte, et pointer sur le fichier dans le

répertoire ou il a été produit

Figure Annexe 6 : Transfert interactif des fichiers des

configurations en mémoire SRAM sur la carte ;

appuyer sur « Transfert ».

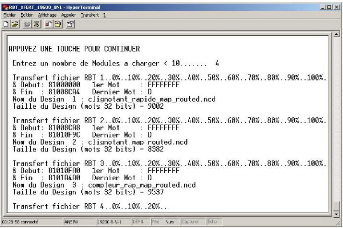

Figure Annexe 7 : Transfert fichier bitstream format .rbt en

cours

3.4 Exemple de début et fin de fichier RBT (module

compteur_rapide)

Figure Annexe 8 : Exemple de début et fin d'un fichier

.RBT

|