3.3.2 Conception sous EDK du module « Système

à processeur »

[26] est un tutorial de référence pour cette

conception. Il s'appuie sur un exemple simple permettant de tester

l'Uart. Quelques autres exemples existent sur le site de Xilinx.

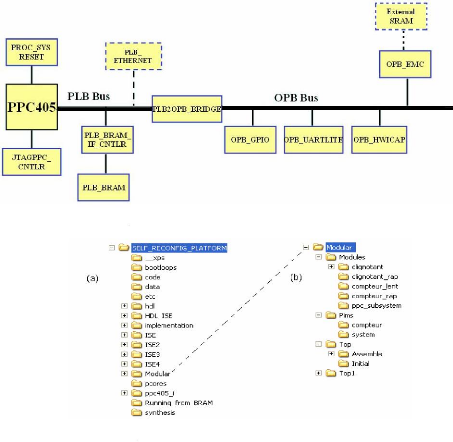

a) Architecture du système

Les différents blocs de cette figure sont disponibles

soit sous forme d'IPs prêts à être implementés

à l'aide des ressources logiques du FPGA, soit directement

présents en blocs ASICs sur la puce FPGA (PPC405, ICAP, JTAG). Les

composantes essentielles de ce système sont :

- Le Processeur PPC405

- Le bus PLB (Processor Local Bus) auquel est directement

relié le processeur ; il est plus

rapide.

- Le contrôleur de BRAM (PLB_Bram_if_ctrl) qui permet

d'associer une BRAM au bus

PLB ; cette BRAM servira de mémoire de données

et/ou de programme au processeur.

- Le bus OPB (On-chip Peripheral Bus) permettant de connecter

les autres périphériques

plus éloignés du processeur.

- Le pont PLB-OPB (Plb2Opb_Bridge) reliant les deux bus.

- Le bloc OPB_GPIO permettant de gérer les

entrées/sorties utilisateurs (LEDs, Switch,

ecran LCD) suivant la plateforme de développement

choisie.

- Le bloc OPB_UARTLite implémentant une interface

série UART allégée qui nous

permettra de faire communiquer le système à

processeur embarqué avec un ordinateur PC via l'application

Hyperterminal sous Windows. Côté PC,

l'HyperTerminal nous permettra d'interagir avec le système

embarqué (à travers le clavier et le terminal

émulés) et d'envoyer les fichiers de configuration au

système à processeur via le port série du PC. Pour cela

nous écrirons côté Processeur PPC405 le programme

permettant ce genre d'échanges de données avec

l'HyperTerminal1.

- Le bloc OPB_HWICAP qui est le contrôleur permettant

d'utiliser le port ICAP.

- Le bloc OPB_EMC qui est le contrôleur de mémoire

extérieur (Flash ou SRAM) ; dans

notre cas, nous avons utilisé une SRAM de 1 Mo externe

à la puce et se trouvant sur la carte de développement

utilisée.

- Le bloc PLB_ETHERNET qui implémente une interface

réseau ; nous n'avons pas

implémenté ce bloc dans le design final car nous

n'en avions pas besoin dans l'immédiat.

b) Création de la plateforme matérielle

du système sous Xilinx EDK

A travers son interface graphique XPS, EDK permet de rajouter

de façon interactive au processeur les blocs présentés

figure 26, et d'unifier tout cet ensemble dans un design unique au niveau top

(qu'il appelle par défaut system.vhd).

Les étapes essentielles sont les suivantes [26] :

- Démarrer XPS (Start ? Programs ? Xilinx Platform

Studio 7.1i ? Xilinx Platform Studio).

- Créer un projet a l'aide "Base System Builder"

XPS (File ? Project ? Base System Builder).

- Choisir un répertoire de travail (par exemple

SELF_RECONF_PLATFORM de la Figure 27, sans espace sur le chemin).

- Choisir la carte de développement ciblée

(dans notre cas c'est la carte Virtex-II Pro P4 FG456 Development

Board de Memec Design).

- Configurer le processeur PPC (on peut laisser les

fréquences par défaut proposées par BSB et choisir 100 Mhz

comme fréquence du bus).

- Choisir les périphériques à utiliser sur

la carte (LEDs, Switches, RS232 Uart, Boutons poussoirs).

1 HyperTerminal est un programme qui permet de se

connecter à d'autres ordinateurs, à des sites Telnet, aux forums

électroniques (BBS), aux services en ligne et aux ordinateurs

hôtes, à l'aide d'un modem, d'un câble null-modem ou d'une

connexion TCP/IP (Winsock).

- Rajouter les périphériques du processeur sur

les bus appropriés suivant le schéma de la Figure 27 (ne

pas oublier de rajouter de la mémoire interne BRAM de 16 ou 32 Ko et de

la mémoire externe SRAM ou Flash de 1 Mo, pour l'instant le bloc

PLB_Ethernet peut ne pas être ajouté).

- Générer la plateforme matérielle.

A l'issue de cette génération interactive de la

plateforme matérielle, XPS aurait ainsi créé dans le

répertoire SELF_RECONF_PLATFORM le fichier projet

system.xmp , les fichiers (.mhs et .mss) décrivant

l'architecture du système et quelques autres répertoires de la

Figure 27(a).

Figure 26 : Architecture du système a

processeur.

Figure 27 : Structure des répertoires du

Projet

Les adresses d'implantations sont attribuées

automatiquement aux différents périphériques dans l'espace

d'adressage du bus auquel ils sont connectés. Mais la plateforme

matérielle (les adresses, les paramètres des blocs IP,

l'Ajout/Suppression de blocs IP, etc...) peut être modifiée

ultérieurement de façon interactive (Project - Add/Edit

Cores....).

c) Création de la plateforme logicielle

Ceci se déroule en deux étapes :

- Génération des pilotes pour les blocs de la

plateforme matérielle ainsi que des librairies

avec la commande Project - Software Platform Setting.

Les fenêtres apparaissant permettent de choisir les versions des

drivers du processeur et des périphériques (laisser les valeurs

par défaut) , les librairies Xilinx à utiliser ( par exemple

cocher Xilnet si on utilise le bloc Ethernet...), le

compilateur à utiliser ( powerpc-eabi-gcc est le compilateur

par défaut), les entrées/sorties standard du processeur

(Stdin/Stdout, ici ce sera l'Uart). Ensuite les librairies

peuvent être générées ( Tools - Generate

Libraries and BSPs).

- Développement des applications pour le processeur

embarqué. Sur la fenêtre System en

haut à gauche sous XPS permettant de voir

l'architecture de la plateforme générée, on peut cliquer

sur Applications pour voir les applications destinées au

processeur. Cette fenêtre permet de créer de nouveaux projets pour

le processeur, d'ajouter les programmes à éxecuter, et d'indiquer

au processeur la mémoire de boot (Bram ou Sram), etc... A ce stade,

Xilinx fournit des programmes simples (hello word, xil_printf,...)

permettant de tester la plateforme en utilisant le clavier et l'ecran d'un PC

comme des entrées/sorties standards du processeur via l'Uart et

l'HyperTerminal.

d) Gestion de la mémoire et

génération du linker script

Notre architecture comprend une mémoire (BRAM) interne

au FPGA et connectée au bus PLB et une mémoire externe SRAM (SRAM

de 1 Mo se trouvant sur la carte d'extension P160 Comm) connectée au bus

OPB. A cause de leur petite taille et de leur distribution sur la puce (il

serait très coûteux en ressources FPGAs de les associer et de les

connecter au bus PLB), les BRAM ne sont pas appropriées comme

mémoire de stockage des bitstreams de configuration. Ces

dernières peuvent etre stockés en SRAM externe.

Le processeur démarre toujours par un programme initial

de boot en BRAM et peut ensuite être dérouté vers

un programme se trouvant en mémoire SRAM externe à l'aide de

XMD1.

Le Linker script est un fichier de script indiquant

les sections du code et les zones mémoires qui les contiendront. Il sert

lors de la compilation du code sous EDK. Lors de la génération

automatique du fichier Linker script, toutes les sections du code sont

automatiquement mises en mémoire BRAM par défaut. Dans notre

application, il est nécessaire de modifier ce fichier pour

1 Xilinx Microprocessor Debugger se

lance sous EDK par Tools - XMD ; il permet de charger en SRAM externe

l'executable .elf et de brancher le processeur sur ce code. En effet, lorsqu'on

fait Tools - Update Bitstream, un programme est chargé par défaut

dans la BRAM interne (Bootloop.c). C'est une boucle infinite 'exécut

é par le processeur. Pour que le processeur BOOT sur un programme il

faut aller a la fenetre «Application», cliquer droit sur le projet

Software concerne et choisir «Initialize BRAM». Le

envoyer certaines sections en mémoire SRAM

externe1 (comme la section .data par exemple car c'est

celle dans laquelle les bitstreams de configurations seront chargées) ;

en effet la BRAM n'est pas assez capacitive pour contenir les fichiers

bitstreams des modules.

e) Implémentation du systeme à

processeur

On peut à présent générer le

fichier bitstreams correspondant à la plateforme matérielle

générée plus haut, afin de configurer le FPGA. Pour cela

il faut choisir ajouter au projet un fichier de contraintes (.ucf)

spécifiant les connexions des les options de projet. A ce stade,

deux cas se présentent :

(i) Déroulement de tout le flot sous EDK afin

de tester et valider le module.

Project - Options - Hierarchy and flow (This is the toplevel

of my design) - Synthesis Tool (ISE XST ) - Implementation tool flow

(XPS_Xflow) - Ok

Tools - Clean , Tools - Generate libraries

Tools - Built user application : génère

l'exécutable destiné au processeur.

Tools - Generate netlist : fait la synthèse de la

plateforne matérielle (fichiers .ngc).

Tools - Generate bitstream : génère le

fichier system.bit permettant de configurer le FPGA et d'y

implémenter la plateforme matérielle de la Figure 26.

Tools - Update bitstream : associe

l'exécutable (.elf) destiné au processeur au fichier

system.bit de configuration du FPGA et génère en fichier

unique download.bit téléchargeable dans le FPGA. Cette

commande lancée toute seule déroule automatiquement les

étapes précédentes de la génération des

librairies à la génération du fichier

download.bit.

A ce niveau, l'outil Impact permet de configurer le

FPGA avec le fichier download.bit. A la fin de la configuration du

FPGA, le processeur exécute le programme chargé en

mémoire. On peut alors vérifier et valider les plateformes

matérielles et logicielles du système.

Remarque: Il peut arriver que le lancement du programmateur de

FPGA depuis XPS échoue ; dans ce cas démarrer l'outil

Impact...

Démarrer-9 Programmes - Xilinx ISE 7.1i -9Accessoires

Æ Impact

...ensuite choisir le mode de programmation (Boundary

Scan par exemple), puis joindre le fichier download.bit et

programmer le FPGA.

programme choisi pour initialiser la BRAM est celui dont

l'exécutable ( .elf) servira a générer le fichier

download.bit.

1 Pour envoyer certaines sections du

code en mémoire SRAM, on peut le faire graphiquement (voir [Xilinx 08])

ou manuellement en éditant le fichier Linker_script et en redirigeant

les sections du type data (.data, .sdata), .sbss, et .text vers la SRAM. Bien

entendu les sections de boot voire la pile (stack) peuvent rester en BRAM pour

accélerer l'exécution.

Le déroulement entier du flot sous EDK

génère les répertoires suivants (Figure

27.a) :

- Le répertoire hdl qui contient les fichiers

vhdl du module system et de ses composantes (IPs). Ces

fichiers sont générés automatiquement à la

génération de la plateforme matérielle sous EDK.

- Le répertoire « Synthesis » qui

contient tous les fichiers de synthèse générés lors

de la génération de la Netlist sous EDK (Tools - Generate

Netlist).

- Le répertoire « Implémentation »

crée par EDK pour stocker tous les fichiers de netlist

nécessaire à implémenter le module fixe

(system).

(ii) Exportation du système à

processeur vers ISE comme module fixe d'un design

global.

Apres avoir testé et validé le module dans un

flot totalement intégré sous EDK, on doit changer les options du

projet afin d'exporter ce module vers ISE comme module fixe du design

Top de la Figure 24 de la façon qui suit:

Project - Options - Hierarchy and flow (This is a submodule

of my design)

- Synthesis Tool (ISE XST ) - Implementation Tool flow

(XPS_Xflow) - Ok

Le processus est ensuite identique au cas (i) ci-dessus

jusqu'à la génération de la netlist (Tools - generate

netlist), suivi par l'exportation du module vers ISE par la commande :

Tools - Export to ProjNav. En effet, dans ce cas de figure, les

bitstreams ne sont pas générés sous EDK.

Remarque : L'exportation du module vers ISE crée

automatiquement un projet ISE s'il n'existe pas encore.

|