3.3 Exemple de mise en oeuvre d'une application

auto-reconfigurable à l'aide

de ISE et EDK

3.3.0 Introduction

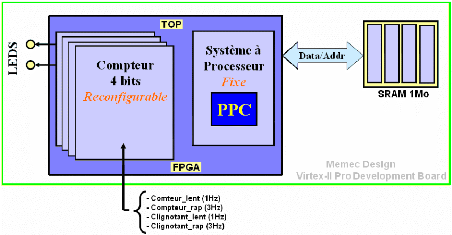

Nous allons détailler les étapes de la mise en

oeuvre de l'auto-reconfiguration à travers une étude de cas. La

Figure 24 présente le schéma de principe de ce

système à deux modules, l'un fixe et l'autre reconfigurable. Les

bitstreams de reconfiguration du module reconfigurable peuvent être

chargés dans une mémoire de type SRAM ou Flash. Le FPGA

utilisé est le VirtexII Pro XVP7 que nous avons présenté

plus haut.

Une fois le FPGA configuré, une application

développée par nous (srp.c) permet au processeur PPC

intégré :

- De charger (via une connexion UART-HyperTerminal a un PC) des

bitstreams partiels

du module reconfigurable et de les stocker en mémoire SRAM

(externe à la puce).

- De reconfigurer dynamiquement et à la demande le module

reconfigurable.

- L'environnement EDK (Embedded Development Kit) de

Xilinx a permis de bâtir

séparément le module fixe (système

à microprocesseur), de développer l'application pour le

processeur et de générer l'exécutable (environnement de

cross-compilation et de debuggage). Xilinx EDK est un ensemble d'outils

softwares pour la conception des systèmes à processeur

embarqué sur des circuits FPGAs Xilinx. A travers son environnement

graphique XPS (Xilinx Platform Studio), EDK facilite la création de

l'architecture matérielle du système a microprocesseur

(processeur et périphériques de communication, Figure

25) et fournit le

support logiciel (generation des pilotes, cross-compilation,

debuggage) permettant le developpement des applications pour le processeur

integre.

- L'environnement ISE (Integrated System Environment) a

permis d'integrer les deux

modules de la Figure 24 dans un design unique

(top.vhd) et de faire la synthèse. En effet, une fois que le

système à processeur est teste et valide sous EDK, il est

exporte vers ISE comme un sous-module reconfigurable afin de construire le

design global de la Figure 24. Après la synthèse du

design global sous ISE, le reste du flot de conception modulaire pour la

reconfiguration partielle (Figure 22) sera deroule par ecriture de

scripts appropries, ce flot n'etant pas automatise sous ISE.

Figure 24 : Etude de cas de l'auto-reconfiguration

3.3.1 La plateforme matérielle de

développement, la carte Virtex-II Pro de Memec Design

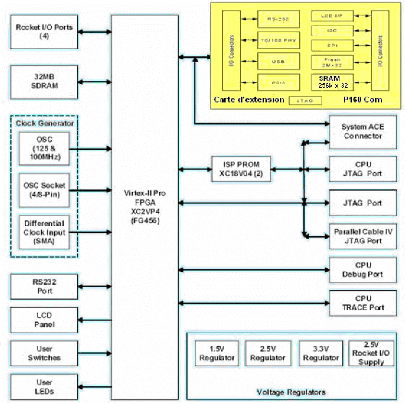

Cette carte developpee par Memec Design comprend essentiellement

(Figure 25): - Un FPGA Virtex II Pro XVP7 ou XVP4

- Une SDRAM 32 Mo que nous n'avons pu utiliser comme memoire de

stockage des

configurations parce qu'elle n'est pas situee du côte du

FPGA où se trouve le module « Système à Processeur

».

- Deux horloges (100MHz et 125 MHz)

- Un ecran d'affichage LCD

- 4 LEDs

- 4 Boutons poussoirs

- 8 DIP switches

- Un port Série RS232 (physiquement connecté au

FPGA par ses pins du côté gauche,

et donc inutilisable par le module « Système à

Processeur » implémenté sur le côté droit de la

puce).

- Un port Jtag

Figure 25 : Vue schématique de la carte de

développement Virtex-II ProTM de Memec Design - Une

carte d'extension P160 Com (Figure 25, en gris).

Cette carte d'extension P160 Com comprend des ressources

additionnelles connectées physiquement aux pins du côté

droit du FPGA sur la carte et donc utilisables par le module «

Système à Processeur » ; ces ressources sont:

- Une mémoire Flash de 8 Mo

- Une mémoire SRAM de 1 Mo (que nous avons

utilisée comme mémoire de stockage

des configurations).

- Un port Ethernet 10/100

- Un port Usb

- Un port série RS232 supplémentaire

- Un port PS/2

- Un écran d'affichage LCD supplémentaire.

[29] est le document de référence de cette

carte.

Mais la limite essentielle de la carte vient de ce qu'elle ne

soit pas adaptée à la reconfiguration partielle. La distribution

des périphériques autour du FPGA ne facilite pas le respect des

contraintes de conception d'applications partiellement reconfigurables. En

effet, comme nous l'avons souligné plus haut, dans ce type

d'application, un module implementé sur le FPGA ne peut utiliser que les

entrées/sorties se trouvant sur la surface qui lui a été

attribuée sur la puce.

|