2.3.2 Configuration du Virtex-II Pro de Xilinx

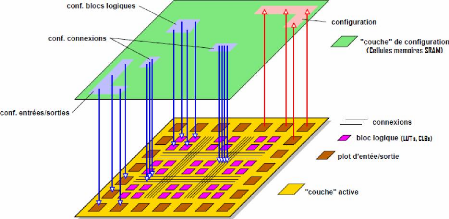

a) Vue en couche d'un FPGA

Le FPGA peut être vu comme une structure à deux

couches (Figure 14):

Figure 14 : Vue en couche d'un FPGA [16]

- Une couche active ou couche logique qui comprend des ressources

logiques, des

entrées/sorties, des ressources de routage, et

éventuellement des blocs dediés.

- Une couche de configuration encore appelée

mémoire de configuration et permettant de

programmer électriquement les caractéristiques

des ressources de la couche active. En effet,

toutes les ressources logiques

du FPGA sont contrôlées par le contenu de la

«mémoire de

configuration» (chez Xilinx cette mémoire

est à base de cellules SRAM1 volatiles, le FPGA doit donc

être reconfiguré à chaque mise sous tension). Leur contenu

fixe l'équation des LUTs, le routage des signaux, les

entrées/sorties et leur tension ainsi que les paramètres de

toutes les autres ressources du FPGA.

Pour programmer un FPGA, les instructions de contrôle de

configuration ainsi que les données à écrire en

mémoire de configuration sont fournies sous forme d'un bitstream qui est

envoyé dans la puce via une interface de configuration (JTAG, SelectMap,

Série,...).

b) Organisation de la mémoire de configuration

et son influence sur la délimitation des modules

reconfigurables

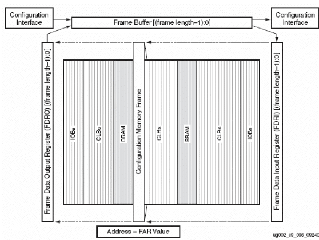

La mémoire de configuration du Virtex-II Pro

est constituée d'un certain nombre de colonnes

élémentaires de mémoires appelées Frames.

Une Frame est la plus petite unité de mémoire

reconfigurable individuellement dans un Virtex-II Pro ; elle est donc

adressable individuellement sur 32 bits et permet ainsi aux FPGAs Xilinx

d'être partiellement reconfigurables2. Une Frame occupe toute

la hauteur du FPGA et chaque ressource programmable (CLBs, IOBs, IOIs, GCLKs,

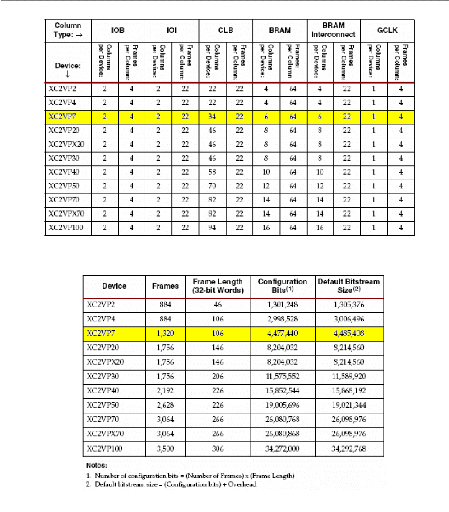

BRAMs) est constituée d'un certain nombre de frames (Error!

Reference source not found.). Le nombre de Frames par ressource ainsi

que la taille de la Frame dépendent

du type de FPGA et fixent la taille du fichier de

configuration totale (Error! Reference source not found.). Par

exemple dans un Virtex-II Pro XVP7 constitué de 1320 frames, on trouve

34 colonnes de CLBs, chacune comprenant 22 frames. A l'aide de la table 3, on

peut refaire le calcul de ce nombre total de frames dans un Virtex-II Pro XVP7

comme suit :

Nbre_Frames_XVP7 = 2x4 IOB_frames + 2x22 IOI_frames + 34x22

CLB_frame

+ 6x64 BRAM_frames + 6x22 BRAMi_frames + 1x4 GCLK_frames =

1320 frames.

Reconfigurer partiellement un FPGA comme le Virtex-II Pro de

Xilinx [24] consiste en la reconfiguration d'une ou plusieurs colonnes (plus

précisement des Frames) de la mémoire de configuration.

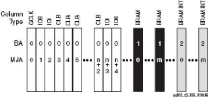

L'alignement en colonne des frames (et donc des ressources) sur la surface

physique du FPGA explique le fait que, dans la reconfiguration partielle, on

attribue exclusivement à un module les I/Os en contact avec la zone du

FPGA attribuée au module. En effet, un module situé à

l'extrémité gauche du FPGA engloberait forcément la

première colonne d'entrées/sorties IOBs (figure 16) et serait

ainsi le seul pouvant utiliser les entrées/sorties du côté

gauche du FPGA.

1 Il est à noter qu'il existe plusieurs technologies

de fabrication des FPGAs, et elles se distinguent généralement

par le type de mémoire de configuration utilisé (SRAM, fuse et

anti-fuse, etc...).

2 La société Atmel propose aussi des FPGAs

à reconfiguration partielle, les AT40K, utilisant un système de

mémoire cache de contextes de configuration très

intéressant pour des applications de notre type.

Table 3 :Répartition des ressources en frames dans les

FPGAs Virtex-II Pro

Table 4 : Taille des données de configuration dans la

série Virtex-II pro

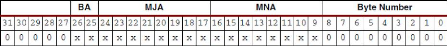

La Figure 15 montre le format d'une adresse de Frame

et la Figure 16 montre le principe d'adressage des Frames. Par

exemple, toutes les adresses ou le mot binaire BA1 = 00 adressent

les colonnes de Frames configurant les GCLK, les IOB, les IOI et toutes les

colonnes

1 Chaque frame de configuration a une adresse unique sur 32

bits composee des champs BA (Block Address), MJA (Major Address) et MNA (Minor

Address) et un octet. Comme indique a la figure 16. BA indexe le bloc de

ressources a configurer (par exemple les blocs BRAM), MJA identifie la colonne

dans le bloc, MNA identifie la frame et l'octet sert de compteur de mots par

frame. Un mot dans une frame ne pourrait etre adresse, voir [Xilinx 06] page

339 pour details.

de CLB alors que pour BA = 01 (resp. 10 ou 2 en decimal) on

adresse les colonnes frames configurant les colonnes BRAM (resp. colonnes de

BRAM INTerconnection). La valeur des bits MJA et MNA permet d'adresser une

frame précise.

Dans un design modulaire, la largeur minimale admissible d'un

module est de 4 Slices (plus précisément 4 colonnes de Slices

correspondant à 2 colonnes de CLBs, car la hauteur d'un module est

toujours égale à celle du FPGA). Reconfigurer partiellement un

module revient à reconfigurer toutes les frames de ses ressources.

Figure 15 : Format d'adresse d'une Frame

Figure 16 : Adressage de la mémoire de

configuration

c) Les modes de reconfiguration

La configuration des FPGAs Xilinx peut être

effectuée de l'extérieur (à partir d'un PC par exemple, ou

d'un microcontroleur) selon les modes suivants :

- Serial (Programmation série).

- JTAG / Boundary-Scan (Programmation via la sonde JTAG). -

SelectMap1 (Programmation parallèle).

Et de l'intérieur par:

- Le port ICAP qui est une interface permettant

d'accéder à la mémoire de configuration du FPGA. Cette

interface est celle que nous avons utilisée pour la reconfiguration

partielle du FPGA par le processeur PPC 405 intégré, mais avant,

le FPGA doit avoir été configuré totalement par l'un des

modes de reconfiguration extérieur cité ci-dessus.

1 SelectMap est une interface de configuration du FPGA depuis

l'exterieur. Il permet d'accéder en lecture/écriture à la

mémoire de configuration du FPGA suivant plusieurs modes. Pour les

détails, voir [Xilinx 06] en page 306.

d) Le port de configuration interne

ICAP

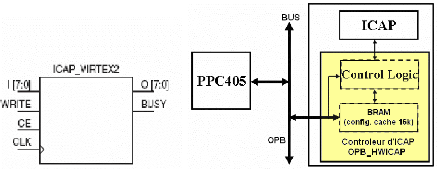

Le port ICAP (Figure 17) est un sous-ensemble de l'interface

SelectMap. Il est physiquement présent sur le FPGA en bas a

l'extrême droite de la puce. Il utilise le même protocole que

SelectMap en mode esclave. Il est capital dans la mise en oeuvre de

l'autoreconfiguration. En effet, il sert d'interface d'accès interne

à toute la mémoire de configuration du FPGA et permet ainsi au

processeur intégré de le reconfigurer partiellement. Dans [24] en

page 317 sont précisées les précautions à prendre

vis-a-vis des autres modes de configuration lors de l'utilisation du port

ICAP.

Figure 17 : Port ICAP Figure 18: Architecture materielle

pour

la reconfiguration via le port ICAP

Pour faciliter l'utilisation de l'ICAP, Xilinx fournit sous

forme d' IP1 un Controleur d'ICAP2 (Figure

178) dont les détails peuvent être trouvés dans [25].

Le contrôleur est instancié comme périphérique du

processeur PPC405 et implemente sous EDK à l'aide des ressources du

FPGA. Il est connecté au bus OPB (On chip Peripheral Bus). Il utilise

une BRAM de 16 Ko (suffisant pour contenir les données de configuration

d'une Frame) qui sert de mémoire de cache aux données de

configuration en provenance du bus pour le port ICAP (reconfiguration) ou vice

versa (Readback) . La BRAM double port est connecté d'un coté au

contrôleur d'ICAP et de l'autre au bus OPB.

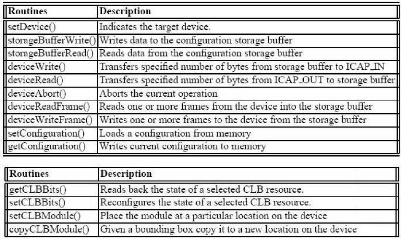

Xilinx fournit également pour le contrôleur une

couche logicielle (pilotes) sous forme de fonctions légères

écrites en C (Error! Reference source not found.) et

évitant d'avoir à gérer la communication entre le bus et

l' ICAP. Par exemple l'écriture en mémoire de configuration du

FPGA se fait en 2 temps (voir table 5):

1 Intellectual Property

2 Sur la figure 17, opb_hwicap est le nom d'instance

choisi pour le contrôleur d'ICAP lors de son implémentation sous

EDK comme périphérique du processeur. De même on le

connecte à un bus (OPB) et on lui attribue une adresse d'implantation

dans l'espace d'adressage du bus.

- La fonction storageBufferWrite( ) permet au

processeur d'écrire un certain nombre de trames binaires (512 mots de 32

bits au maximum pour les 16Ko de BRAM) en BRAM de cache.

- La fonction deviceWriteFrame( ) permet ensuite au

contrôleur de transférer ces trames précédemment

écrites en BRAM vers le port ICAP qui les interprètent pour

configurer le FPGA frame par frame. Ces trames proviennent des bitstreams de

configuration partielle du FPGA et contiennent toutes les informations

nécessaires à l'adressage et à la configuration d'une ou

plusieurs frames.

Les fonctions storageBufferRead( ) et

deviceReadFrame( ) jouent respectivement le même rôle que

les deux précédentes mais plûtot dans le sens ICAP -

Processeur PPC405 et servent donc à lire le contenu des frames du FPGA

(Readback).

Table 5 : Fonctions permettant de lire et écrire en

mémoire de configuration via le port ICAP

Figure 19 :L' Interface de configuration du Virtex-II Pro et

ses registres

e) Analyse des trames de

configuration1

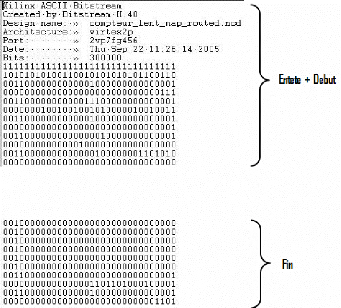

1 Premieres et les dernieres lignes d'un fichier bitstream au

format ASCII (.rbt)

Comme expliqué plus haut, configurer le FPGA revient

à y envoyer à l'interface de configuration (Figure 19)

un fichier bitstream de configuration sous forme de trames qui comprennent les

données de contrôle de configuration et les données

à écrire dans les frames de configuration pour programmer les

ressources. On distingue globalement:

- Les trames d'écriture

- Les trames de lecture

- Les trames de synchronisation

- Etc...

[23] étudie en détails au chapitre 4 toutes ces

trames et les registres cités dans l'exemple cidessous.

Les premières et les dernières lignes (il peut

en avoir plusieurs milliers de lignes suivant la taille du module) d'un exemple

de fichier bitsteam au format RBT apparaît plus haut. Il permet de

reconfigurer un module du FPGA. Ce sont donc des trames d'écriture. Nous

l'avons généré dans le cadre de ce projet. La trame de

reconfiguration commence en ligne 8. On peut décrypter ces quelques

lignes de trames comme suit [23] :

- Les 7 premières lignes représentent

l'entête du fichier RBT ; elles renferment quelques renseignements.

- 0xff, 0xff, 0xff, 0xff : Mot inutile (ligne 8).

- 0xaa, 0x99, 0x55, 0x66 : Mot de synchronisation. Demande au

FPGA de commencer à analyser les mots suivants.

- 0x30, 0x00, 0x80, 0x01 : Mot d'entête ; annonce une

écriture de 1 mot dans le registre de commandes.

- 0x00, 0x00, 0x00, 0x07 : Remise à zéro du

registre du CRC.

- 0x30, 0x01, 0xc0, 0x01 : Mot d'entête. Annonce

l'écriture du code d'identification du FPGA (registre IDCODE).

- 0x01, 0x24, 0xa0, 0x93 : Code d'identification du FPGA

- 0x30, 0x00, 0x80, 0x01 : Mot d'entête. Annonce une

écriture de 1 mot dans le registre de commande (registre CMD).

|

- 0x00,

|

0x00,

|

0x00,

|

0x01 : Initialise l'écriture des données de

configuration

|

|

- 0x30,

|

0x00,

|

0x20,

|

0x01 : Mot d'entête. Annonce l'écriture de

l'adresse de la colonne

|

élémentaire.

- 0x00, 0x48, 0x0c, 0x00 : Adresse de l'unité

élémentaire à reconfigurer (voir figure 15 et figure

16).

- 0x30, 0x00, 0x40, 0xd4 : Mot d'entête. Annonce

l'écriture de 212 mots de 16 bits de configuration. Nous indiquons ici

la taille de l'unité élémentaire spécifique

à chaque FPGA.

- En fin de fichier on a toujours la même séquence

de trames, et le mot de fin est 0x00, 0x00, 0x00, 0x0D.

|