2.3 Les divers scénarii de reconfiguration des

FPGAs

2.3.1 Les modèles de reconfiguration [4]

Un facteur de différenciation des FPGAs est leurs modes

(ou possibilités) de

configurations qui varient d'une famille à l'autre. Ces

modes sont souvent liés à la technologie de fabrication et

peuvent être des critères déterminants lors du choix du

FPGA cible pour implémenter une application. Par exemple pour une

application nécessitant plusieurs configurations (contextes), il peut

être profitable d'utiliser un FPGA reconfigurable dynamiquement

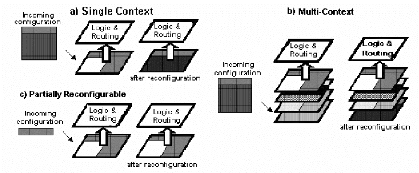

(RTR-Runtime Reconfigurable). Comme décrit dans [4], on peut

classifier les architectures reconfigurables en trois catégories suivant

leurs modèles de reconfiguration (Figure 12). Ces

modèles qui s'appliquent également aux FPGAs sont:

a) La reconfiguration à contexte unique

(Single Context)

Elle est encore appelée Reconfiguration totale car la

reconfiguration se fait entièrement sur toute la surface de la matrice

de configuration (sur tout le FPGA par exemple). Tous les bits de la matrice de

configuration sont donc réécrits, même s'ils n'ont pas

changé entre deux configurations (Figure 12.a). Ce qui est

évidemment une perte de temps. La reconfiguration à contexte

unique est utilisée pour des applications statiquement

reconfigurables (SRD - Statically Reconfigurable Design). Plusieurs

applications sont programmées une à la fois (par chargement du

fichier binaire correspondant) sur le FPGA; un Reset du FPGA est

effectué entre deux programmations.

b) La reconfiguration multi-contextes

(Multi-Context)

Elle se fait sur des FPGAs ayant plusieurs mémoires de

configuration se trouvant sur des plans différents (Figure

12.b). On peut ainsi "charger" plusieurs plans de configurations dans le

FPGA, et le passage d'une configuration à l'autre (commutation de

contexte) se fait par commutation d'un plan mémoire à un autre.

Par rapport à la reconfiguration à contexte unique,

1 Memoires de données et des programmes

separées et accessibles par des bus séparés

également, ce quipermet l'accès simultanée des

données et des programmes, contrairement a l'architecture de Von

Neumann. Ceci

le temps de reconfiguration en est fortement

accéléré. En outre, une mémoire inactive peut

être reprogrammé pendant que l'autre est active sur le FPGA. Une

sorte de mémoire cache de contexte existe alors dans le FPGA.

Ce type de reconfiguration s'apparente au Page Mode

[1] dans les séries Stratix et APEX 20K d'Altera où on peut

charger jusqu'à 8 configurations en mémoire Flash et passer

dynamiquement d'une à l'autre. Dans ce cas la mémoire Flash est

divisée en pages, chaque page contenant un bitstream1 total

pouvant configurer tout le FPGA ; il ne s'agit pas de plan de configuration, et

donc pas d'accélération de temps de reconfiguration.

Figure 12 : Les différents types de reconfiguration

[4]

c) La reconfiguration partielle ( Partially

Reconfigurable)

Contrairement à la reconfiguration à contexte

unique ou multi-contextes, on peut configurer partiellement le FPGA afin de

n'utiliser que les ressources nécessaires à

l'implémentation de l'application (Figure 12.c) ; on reduit

ainsi la consommation en énergie et en ressources logiques du FPGA,

ainsi que le temps de reconfiguration.

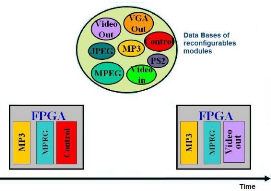

En outre, une portion du FPGA peut être

reconfigurée dynamiquement (c'est-à-dire reconfigurer une partie

du FPGA pendant que l'autre active), ce qui cache la latence due à la

reconfiguration qui peut s'observer dans la reconfiguration à contexte

unique ou multiple. Reconfigurer dynamiquement permet l'implémentation

matérielle de beaucoup plus de sections de l'application et

d'accélerer ainsi l'exécution. Par exemple sur la Figure

13, le module «Control » est remplacé par le

module « Video out » par reconfiguration partielle du

FPGA.

accelère l'execution et est tres utilisé dans

les processeur de type DSP

1 Fichier de flot de données contenant une

configuration prête à être chargée dans le FPGA. Dans

le cas du Virtex, il peut être en .bit pour le binaire ou en .rbt pour

son equivalent ASCII. L'Outil de programmation de FPGA (Impact par exemple)

supporte indifféremment l'un ou l'autre type de fichier pour la

reconfiguration.

Figure 13 Reconfiguration partielle et dynamique du

FPGA

|