4.2 Conclusion

Ce rapport a montré la faisabilité de l'auto

reconfiguration partielle et dynamique sur un FPGA Virtex-II Pro. Ce travail

s'inscrit dans le cadre de la recherche sur les architectures reconfigurables

dynamiquement. Il est une contribution à la définition d'une

méthodologie permettant de tirer le meilleur profit de la

reconfiguration partielle des FPGAs.

Nous avons souligné dans les chapitres 1 et 2 de ce

rapport les avantages et les limites de l'implémentation d'une

application sur un processeur (grande flexibilité au prix de

performances moindres) ou sur un ASIC (grandes performances au prix d'une

faible flexibilité). Nous avons évoqué le meilleur

compromis flexibilité/performance qu'offraient les architectures

reconfigurables dynamiquement en général et les FPGAs en

particulier.

Ce type d'architecture est une des solutions qui permettront

de répondre aux exigences des systèmes embarqués du futur.

La reconfiguration dynamique est en train de combler l'écart entre et le

logiciel et le matériel. Et le FPGA singulièrement profite

beaucoup plus des avancées technologiques. Leur densité

(jusqu'à 10 millions de portes) et leurs performances (200Mhz)

continuent de croître très vite, et on parle de plus en plus de

conception à base de FPGA (FPGA Based Design).

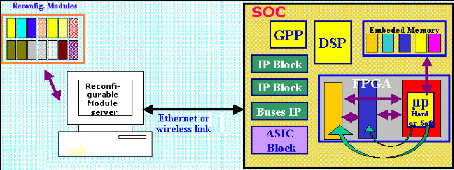

La figure ci-dessous (figure 30) représente un exemple

de SOCs hétérogènes du futur. Une plate-forme comme la

notre est nécessaire à la mise en oeuvre d'un OS

dédié à la gestion de la ressource FPGA. L'architecture

globale du SOC évoluerait pour s'adapter aux traitements à

effectuer. Les applications sont nombreuses dans le domaine de la

téléphonie mobile de 3ème et 4ème géneration

par exemple, meme s'il y a encore des blocages lies a la consommation en

puissance des FPGAs.

D'autre part, l'essor des architectures reconfigurables passe

par le développement des nouveaux outils et méthodes conception

qui pour l'instant semblent en retard sur la technologie.

La figure ci-dessous (figure 30) représente les SOCs

hétérogènes du futur. Une plate-forme comme la notre est

nécessaire à la mise en oeuvre d'un OS dédié

à la gestion de la ressource FPGA.

Enfin, l'essor des architectures reconfigurables passe par le

développement des nouveaux outils et méthodes conception qui pour

l'instant semblent en retard sur la technologie.

Figure 30 : SOC hétérogéne

4.3 Perspectives

4.3.1 Implémenter les bus macros pour les connexions

inter-modules.

Les bus-macros sont les seuls moyens de connexion entre de

deux modules d'un design partiellement reconfigurable. Nous n'avons pas eu le

temps d'en implémenter dans cette application, notre but premier

étant de valider le concept d'auto reconfiguration. De nombreux exemples

d'implémentation de bus macros existent, et peuvent être

expérimentée sur notre plate-forme de démonstration.

|