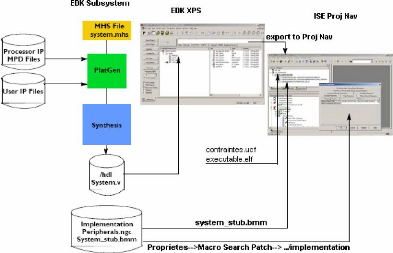

3.4 Récapitulatifs

Nous avons implémenté et testé

l'auto-reconfiguration sur le virtex-II Pro. Le processus étant assez

touffu, la Figure 28 ci-dessus donne un rapide aperçu de la

démarche.

1. Sous EDK_XPS une plate-forme matérielle

(intégrant le processeur) est générée suivant un

flot standard intégré.

2. Sous EDK_XPS la plateforme logicielle est

développée et testée sur la plateforme matérielle

générée ; l'exécutable (.elf) est

produit.

3. La plate-forme matérielle ci-dessus est

exportée vers ISE Proj_Nav comme un module d'un design à

plusieurs modules. Ce design est synthétisée suivant les

étapes et les règles (.ucf, .ngc) du Modular Design pour la

reconfiguration partielle.

4. Les bitstreams partiels et complets sont

générés. On peut alors éditer le design

routé du module importé de EDK vers ISE à l'aide de

FPGA Editor afin de localiser les coordonnées des BRAMs et

éditer le fichier system.bmm en s'inspirant du fichier

system_stub.bmm comme indiqué en annexe 2.

5. On associe les fichiers .bit, .elf et .bmm

pour générer le bitstream final.

Figure 28 : Flot de conception de l'ensemble de la

plateforme.

|