3.1.3 Le Modular Design Flow pour la reconfiguration

partielle

a) Présentation [22]

Il s'agit d'une méthode de conception

incrémentale. A l'origine il permet à une équipe

d'ingénieurs de travailler indépendamment sur des modules d'un

design en vue d'une fusion postérieure et une implémentation sur

un FPGA unique. Comme décrit au paragraphe précédent, un

grand design est découpé en plusieurs modules en vue d'un travail

en équipe. Chaque concepteur de l`équipe implémente et

teste le(s) module(s) à sa charge séparément, et le chef

d'équipe définit la structure globale du design et intègre

les modules implémentés au niveau Top-Level du design

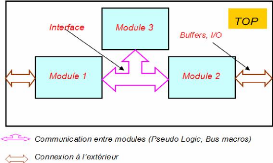

qui comprend (Figure 21) :

Figure 21 : Vue au niveau TOP d'un design modulaire

- Un ensemble de modules indépendants (mais synchrones et

pouvant communiquer par des interfaces appelés Bus macros).

- L'interface entre les modules (Bus macros).

- L'interface avec les pins (les E/S du design sont

déclarées au niveau Top).

Un fichier de contrainte (.ucf chez Xilinx) permet de

fixer les contraintes d'espace (pour les pins du FPGA à utiliser et la

position de chaque module sur le FPGA) et de temps (fréquence maximale

de fonctionnement). Chez Xilinx, ce fichier peut être soit écrit

soi-même, soit généré automatiquement par l'outil

Floorplaner, l'éditeur graphique de contraintes d'espace pour

les FPGAs Xilinx.

b) Modular Design Flow pour la reconfiguration

partielle

Le Modular Design flow par son approche modulaire est

particulièrement adapté à la conception d'applications

partiellement reconfigurables comme la nôtre ou un module entier

doit être reconfiguré. Mais le modular design flow pour la

reconfiguration partielle suggère pour des raisons pratiques que

toute conception doit avoir au niveau top deux parties homogènes

(à ne pas confondre avec les modules dont le nombre maximal est en

théorie égale au quart du nombre de colonnes de Slices) : une

partie fixe et une partie reconfigurable.

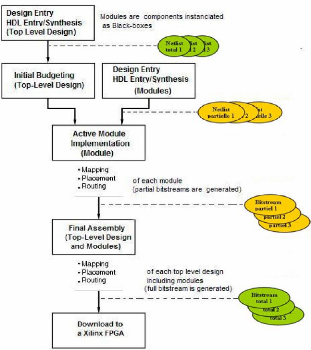

Figure 22 : Le flot Modular Design pour la reconfiguration

partielle Il se déroule en 4 étapes (Figure 22)

:

1. La Synthèse des modules et du design au niveau

top (Top-level Design).

2. L'Initial Budgeting qui détermine

approximativement la taille de chaque module à implémenter puis

lui attribue une zone sur le FPGA conformément aux contraintes de

placement et de temps.

3. L'Active Module Implémentation ; les

modules sont implémentés individuellement et dans des

répertoires séparés, et les bitstreams partiels sont

générés dans le cas de la reconfiguration partielle.

4. Le Final Assembly qui implémente le design

entier en assemblant tous les modules, puis génère son bitstream

complet qui permet de configurer le FPGA.

Nous décrirons en détail les étapes du

Modular Design dans un cas d'étude effectué plus loin.

|