Mémoire :

Mise en OEuvre de l'auto reconfiguration

partielle

et dynamique sur un FPGA Xilinx Virtex-II

Pro

Présenté par :

Guy WASSI

LEUPI

En vue de l'obtention du :

Spécialité :

Informatique Industrielle et

Systèmes

Automatisés (IISA)

Laboratoire d'accueil

ETIS

ENSEA - Université de Cergy

Soutenu le 07 Mars 2006

Jury :

Michel Drouin, Président

Véronique Perdereau, Responsable de la

formation

Amine Benkhelifa, Encadrant de stage

RESUME

Pour faire face à la complexité algorithmique et

aux exigences de flexibilité des applications futures (systèmes

de radio Communication 3G et 4G par exemple), de nouvelles approches doivent

être envisagées dans la conception des architectures

numériques. Dans ce contexte, les architectures reconfigurables

dynamiquement présentent des atouts considérables car elles

offrent le meilleur compromis Flexibilité/Performance. Les FPGAs (Field

Programmable Gate Array) sont les composants reconfigurables les plus denses et

flexibles, permettant des manipulations au niveau bit. Aujourd'hui, il existe

des plateformes mixtes (FPGA et Processeur intégré dans un SOC

unique une seule puce) permettant d'envisager l'auto-reconfiguration partielle

du FPGA sous le contrôle de son processeur embarqué. Dans une

telle configuration, la partie FPGA serait un accélérateur

matériel dont les fonctionnalités évolueraient et

s'adapteraient aux contextes, et ce sans interruption de service.

Mais les environnements de développement fournis par

les constructeurs de telles plateformes n'intègrent pas encore le flot

de conception des applications auto-reconfigurables. Certes les outils tels que

JBits API (Application Programming Interface) permettent de manipuler

sélectivement les ressources configurables des FPGAs Xilinx à

partir d'un PC. Mais JBits nécessite que JVM (Java Virtuel Machine)

tourne sur le processeur hôte, ce qui peut ne pas être souhaitable

dans le cas d'un système embarqué.

Ce rapport présente la mise en oeuvre d'une approche

modulaire (Modular Design Flow) de l'auto-reconfiguration dynamique et

partielle sur un FPGA Virtex-II Pro de Xilinx, le processeur PPC405

intégré reconfigurant dynamiquement et partiellement le FPGA via

un port interne. Pour cela nous avons développé une application

basée sur une API1 ICAP de Xilinx écrite en C et

permettant de lire/écrire/modifier la mémoire de configuration du

FPGA via l'interface interne ICAP (Internal Configuration Access Port). Bien

entendu cette API est assez légère pour tourner sur le processeur

PPC405 embarqué.

1 Application Programming

Interface

SOMMAIRE

|

Sommaire

Abréviations

Liste des figures

Liste des tableaux

Remerciements

|

2

5

5

6

5

|

|

1

|

INTRODUCTION

|

8

|

|

1.1

|

Le Contexte

|

8

|

|

1.2

|

But du stage

|

9

|

|

1.3

|

Travaux similaires

|

10

|

|

1.4

|

Environnement de travail

|

10

|

|

1.5

|

Plan du rapport

|

11

|

|

2

|

FPGA, RECONFIGURATION DYNAMIQUE ET CONCEPTION DE SYSTEMES

|

12

|

|

EMBARQUES

|

|

|

2.0

|

Introduction

|

12

|

|

2.1

|

Implémentation logicielle vs implémentation

matérielle d'une application

|

14

|

|

2.1.1

|

Implémentation logicielle

|

14

|

|

2.1.2

|

Implémentation matérielle

|

14

|

|

2.1.3

|

Partitionnement Matériel / Logiciel

|

15

|

|

2.2

|

Architecture des FPGAs (Field Programmable Gate Array)

|

16

|

|

2.2.1

|

Introduction

|

16

|

|

2.2.2

|

Principe de fonctionnement et Architecture Interne des FPGAs

|

16

|

|

2.2.3

|

Exemple d'architecture de FPGA : la série Virtex-II Pro de

Xilinx

|

18

|

|

2.2.4

|

Détails de quelques unes des ressources du Virtex-II Pro

|

19

|

a)

|

Les CLBs (Configurable Logic Blocks - Blocs de logiques

configurables)

|

19

|

b)

|

Les SLICES

|

19

|

c)

|

|

Les blocs multiplieurs 18 x 18 bits

|

20

|

|

|

d)

|

Le processeur PowerPC 405

|

21

|

|

2.3

|

Les divers scenarii de reconfiguration des FPGAs

|

22

|

|

2.3.1

|

Les modèles de reconfiguration

|

22

|

a)

|

La reconfiguration à contexte unique (Single Context)

|

22

|

b)

|

La reconfiguration multi-contextes (Multi-Context)

|

22

|

c)

|

|

La reconfiguration partielle ( Partially Reconfigurable)

|

23

|

|

|

2.3.2

|

Configuration du Virtex-II Pro de Xilinx

|

24

|

|

a)

|

Vue en couche d'un FPGA

|

24

|

b)

|

Organisation de la mémoire de configuration et son

influence sur la délimitation des modules reconfigurables

|

25

|

|

c)

|

Les modes de reconfiguration

|

27

|

|

d)

|

Le port de configuration interne ICAP

|

28

|

|

e)

|

Analyse des trames de configuration

|

30

|

|

3

|

METHODOLOGIES DE MISE EN OEUVRE DE L'AUTO-RECONFIGURATION

|

32

|

|

PARTIELLE ET DYNAMIQUE SUR LE VIRTEX-II PRO

|

|

|

3.1

|

Méthodologie de conception

|

33

|

|

3.1.1

|

Flot de conception standard (Ordinary Design Flow)

|

34

|

|

3.1.2

|

Le Flot de conception incrémentale (Incremental Design

Flow)

|

35

|

|

a)

|

La synthèse incrémentale

|

36

|

|

b)

|

Le Placement et Routage (P&R) Incrémental

|

36

|

|

3.1.3

|

Le Modular Design Flow pour la reconfiguration partielle

|

36

|

a)

|

Présentation

|

36

|

b)

|

|

Modular Design pour la reconfiguration partielle

|

37

|

|

|

3.2

|

Principe de l'Auto-Reconfiguration partielle et dynamique

|

38

|

|

3.2.1

|

De la reconfiguration partielle

|

38

|

|

3.2.2

|

De l'auto-reconfiguration dynamique

|

39

|

|

3.3

|

Exemple de mise en oeuvre d'une application auto-reconfigurable

sous ISE et EDK...

|

39

|

|

3.3.0

|

Introduction

|

39

|

|

3.3.1

|

La plateforme matérielle de développement, la carte

Virtex-II Pro de Memec Design

|

40

|

|

3.3.2

|

Conception sous EDK du module << Système a

processeur »

|

42

|

|

a)

|

Architecture du système

|

42

|

|

b)

|

Création de la plateforme matérielle du

système sous Xilinx EDK

|

43

|

|

c)

|

Création de la plateforme logicielle

|

45

|

|

d)

|

Gestion de la mémoire et génération du

linker script

|

45

|

|

e)

|

Implémentation du système à processeur

|

46

|

|

3.3.3

|

Conception sous ISE du design global <<Top » suivant

le Modular Design Flow

|

47

|

a)

|

Création des codes sources

|

47

|

b)

|

|

Etape de synthèse des fichiers sources

|

48

|

|

|

c)

|

Etape d'Initial Budgetting

|

50

|

|

d)

|

Etape d'Active Module Implémentation

|

51

|

|

e)

|

Etape de Final Assembly

|

52

|

|

f)

|

Etape de génération du bistream final

|

52

|

|

3.4

|

Récapitulatifs

|

53

|

|

4

|

DIFFICULTES RENCONTREES, CONCLUSION ET PERSPECTIVES

|

55

|

|

4.1

|

Difficultés rencontrées

|

55

|

4.1.1

|

Les restrictions physiques à la reconfiguration partielle

des FPGAs Xilinx

|

55

|

|

4.1.2

|

Les outils

|

56

|

|

4.2

|

Conclusion

|

57

|

|

4.3

|

Perspectives

|

58

|

|

4.3.1

|

Implémenter les bus macros pour les connexions

inter-modules

|

58

|

|

4.3.2

|

Utiliser XMS , le fichier de système de Xilinx

|

58

|

|

4.3.3

|

Implanter l'interface de Ethernet

|

58

|

|

4.3.4

|

OS temps réels pour la gestion de la ressource FPGA

|

59

|

|

A.

|

ANNEXES

|

60

|

|

A-1

|

ANNEXE 1: Les Outils

|

60

|

|

A-1.1

|

L'outil Floorplanner (Editeur de contraintes de placement, cas de

2 modules)

|

60

|

|

A-1.2

|

FPGA Editor (Routage avec bitstream complet)

|

60

|

|

A-2

|

ANNEXE 2: Procédure de création du fichier

SYSTEM.BMM

|

61

|

|

A-2.1

|

Fichier system_stub.bmm

|

61

|

|

A-2.2

|

Le fichier system.bmm

|

62

|

|

A-3.

|

ANNEXE 3: Utilisation de la Plate-forme de démonstration

|

62

|

|

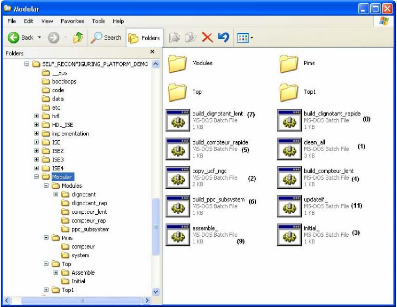

A-3.1

|

Génération des bitstreams à partir des du

répertoire Modular

|

62

|

|

A-3.2

|

Paramètres de configuration de l'HyperTerminal

|

63

|

|

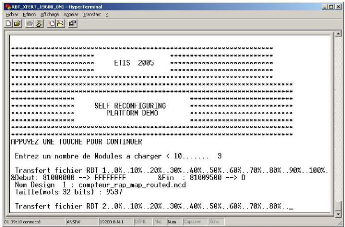

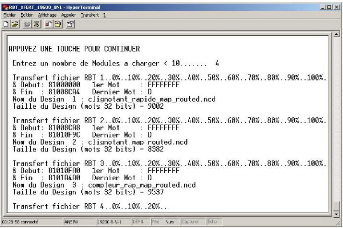

A-3.3

|

Message d'accueil de la demo

|

64

|

|

A-3.4

|

Exemple de début et fin de fichier RBT (module

compteur_rapide)

|

65

|

|

A-4.

|

ANNEXE 4 : Listing des programmes

|

66

|

|

A-4.1

|

Le code VHDL du Top (top.vhd)

|

66

|

|

A-4.2

|

Code VHDL d'un design du module reconfigurable

(compteur_lent.vhd)

|

69

|

|

A-4.3

|

Fichier de contraintes (top.ucf)

|

71

|

|

A-4.4

|

Les codes sources des programmes développés en C

pour le processeur PPC405.

|

73

|

|

A-4.5

|

Les fichiers de commande .batch pour le Modular

Design Flow

|

82

|

|

RÉFÉRENCES BIBLIOGRAPHIQUES

|

85

|

ABREVIATIONS

ASIC : Application-Specific Integrated Circuit BRAM : BlockRAM

CLB : Configurable Logic Blocks

CPU : Central Processing Unit

EDK : Embedded Development Kit FPGA : Field Programmable Gate

Array GPP : General Purpose Processors ICAP : Internal Configuration Access

Port LUT : Look Up Table

OPB : On-chip Peripheral Bus

RISC : Reduced Instruction Set Computer rSOC : reconfigurable

System-On-a-Chip SOC : System-On-a-Chip

SOPC : System-On-a-Programmable-Chip

UART : Universal Asynchronous Receiver-Transmitter

UCF : User Constraints File

XPS : Xilinx Platform Studio

VHDL : Very High Speed Integrated Circuit Hardware

Description Language

Liste des figures

Figure 1 : Exemple de Systèmes Embarqués 13

Figure 2 : Evolution des systèmes électroniques

13

Figure 3 : Implémentation temporelle vs

implémentation spatiale 14

Figure 4 : Structure globale des FPGAs 17

Figure 5 : Un LUT (Look-Up-Table) 17

Figure 6 : Implémentation d'une fonction Y = ab + (non)C

17

Figure 7 : Structure interne d'un CLB 20

Figure 8 : Structure interne d'un Slice 20

Figure 9 : Bloc multiplieur et SelectRam 20

Figure 10 : Vue générale du Virtex-II Pro XVP7

20

Figure 11 : Structure générale du processeur

PowerPC 405 21

Figure 12 : Les différents types de reconfiguration

23

Figure 13 : Reconfiguration partielle et dynamique du FPGA 24

Figure 14 : Vue en couche d'un FPGA 24

Figure 15 : Format d'adresse d'une Frame 27

Figure 16 : Adressage de la mémoire de configuration

27

Figure 17 : Port ICAP 28

Figure 18 : Architecture matérielle pour la

reconfiguration via le port ICAP 28

Figure 19 : L' Interface de configuration du Virtex-II Pro et ses

registres 30

Figure 20 : Flot de conception Standard pour les FPGAs 35

Figure 21 : Vue au niveau TOP d'un design modulaire 36

Figure 22 : Le flot Modular Design pour la reconfiguration

partielle 37

Figure 23 : Passage d'un Top à un autre par

reconfiguration partielle 38

Figure 24 : Etude de cas de l'auto-reconfiguration 40

Figure 25 : Vue schématique de la carte de developement

Virtex-II ProTM de Memec 41

Design

Figure 26 : Architecture du systeme a processeur 44

Figure 27 : Structure des répertoires du Projet 44

Figure 28 : Flot de conception de l'ensemble de la plateforme

54

Figure 29 : Vue physique de la carte Virtex-II Por de Memec

Design 56

Figure 30 : SOC hétérogène 58

Liste des tables

Table 1 : Comparatif des caractéristiques de

différentes implémentations 15

Table 2 : FPGAs de la famille Virtex-II Pro et leurs principales

ressources 19

Table 3 : Répartition des ressources en frames dans les

FPGAs Virtex-II Pro 28

Table 4 : Taille des données de configuration dans la

série Virtex-II pro 28

Table 5 : Fonctions permettant lire et écrire en

mémoire de configuration via le port 28

ICAP

Table 6 : Principaux fichiers générés au

déroulement du Modular Design Flow 29

REMERCIEMENTS

Je remercie tout particulièrement Monsieur Amine

Benkhelifa de m'avoir permis d'effectuer ce stage sous sa supervision, mais

surtout pour son aide précieuse, sa disponibilité, et toute son

expérience dont il a su me faire profiter tout au long de mon stage.

Je tiens à remercier également Monsieur Francois

Verdier pour ses constants éclaircissements et sa disponibilité

dont j'espère vivement n'avoir pas abusée.

Ma gratitude s'adresse également à Arthur Segard

qui m'a soutenu au quotidien et qui a certainement subi plus que toute autre

personne mes incessantes questions.

Je remercie également tous les autres membres du

Laboratoire ETIS pour l'esprit de convivialité qui règne en son

sein et qui a facilité mon intégration.

Je remercie enfin les membres du jury qui ont bien voulu assister

à mon exposé.

1. INTRODUCTION

1.1 Le contexte

Les besoins sans cesse croissants des systèmes

embarqués en puissances de calcul incitent à l'exploration de

nouvelles architectures. En effet, pour palier aux limites des processeurs

génériques ou spécifiques une solution est l'utilisation

d'architectures dédiées comme accélérateurs

matériels pour certaines tâches. Aujourd'hui, l'une des solutions

semblent être la mise en oeuvre d'architectures alliant dans une moindre

mesure la flexibilité des processeurs et la performance des circuits

spécialisés ASICs1 : Ce sont des architectures

reconfigurables. Cette approche est possible grâce aux avancées

technologiques qui permettent d'une part la mise en oeuvre des SOCs

(System-On-a-Chip, intégration sur une puce unique toutes les

fonctionnalités de traitement numérique des informations telles

que processeurs, DSP, mémoires, bus, blocs dédiés, etc...)

et d'autre part de fabriquer des circuits programmables FPGAs de plus en plus

denses et sophistiqués.

En effet, jusqu'alors essentiellement destinés au

prototypage rapide des ASICs (à cause des limites dues à leur

vitesse lente, leur coût et leur consommation élevés),

l'utilisation des FPGAs comme ressource matérielle de calcul

reconfigurable dynamiquement est aujourd'hui sérieusement

envisagée. Dans cette optique, le projet ARDOISE2 par exemple

a prouvé l'efficacité de la reconfiguration successive sur une

même architecture de type FPGA des opérateurs d'une chaîne

de traitement de flux vidéo.

Aujourd'hui, la densité croissante des FPGAs

(jusqu'à 10 millions de portes...) et leur possibilité de

reconfiguration rapide et dynamique ouvrent de nouvelles perspectives.

Des plateformes hétérogènes SOPC

(System-On-a-Programmable-Chip) comme les produits Xilinx Virtex-II Pro ou

Altera Excalibur-Arm intégrant des zones reconfigurables et des

processeurs de traitement généralistes (PowerPC405 ou ARM920)

permettent d'envisager la construction de systèmes auto-reconfigurables

dynamiquement : le processeur de la puce provoquant lui-même la

reconfiguration (partielle dans certains cas) du FPGA. Il devient ainsi tout

à fait envisageable de mettre en oeuvre des architectures SOC hybrides

dans lesquelles certaines tâches seraient implémentées

matériellement et gérées suivant le modèle des

tâches logicielles dans un OS (ordonnancement, commutation de

tâches, préemption de tâches, etc...).

1 Application-Specific Integrated Circuit; circuit

intégré optimisé pour une application

spécifique.

2 ARDOISE Architecture Reconfigurable Dynamiquement

Orientée Image et Signal,

Ce type d'architectures hybrides où les tâches

s'exécuteraint sous forme matérielle et/ou logicielle offrirait

d'une part une flexibilité supplémentaire et d'autre part

permettrait l'utilisation de toutes les unités de calcul (Processeur,

DSP, FPGA, etc.).

1.2 But du stage

La problématique globale de ce stage est la mise en

oeuvre de l'auto-reconfiguration partielle et dynamique sur une plateforme SOPC

intégrant sur une même puce processeur(s) et FPGA. En effet, la

technologie n'étant pas encore mature surtout au niveau de la mise au

point d'outils permettant d'automatiser cette mise en oeuvre, notre but est de

montrer la faisabilité de l'«Auto-reconfiguration partielle et

dynamique » à l'aide d'outils de développement

disponibles.

Nous entendons ici par Auto-reconfguration partielle et

dynamique le fait pour le processeur intégré1 au

FPGA de reconfigurer partiellement ce dernier sans perturber le fonctionnement

continu de la zone non reconfigurée.

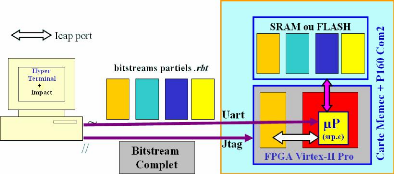

Ci-dessous2 (figure) se resument les choix faits

à priori :

- Configurer totalement le FPGA avec un design modulaire

(developpé suivant le Modular Design Flow approprié

à la reconfiguration partielle) depuis un PC par les moyens classiques

et éprouves.

- Générer sur PC les bitstreams partiels pour le(s)

module(s) reconfigurable(s).

- Dévélopper une application (srp.c) pour

le processeur PPC405 intégré permettant à ce dernier de

communiquer avec le PC via le port serie et l'application

Hyperterminal afin de

Embarquée AC! soutenue par le MESR en 1998 et

1999.

www-etis.ensea.fr/Equipes/Archi

1 Chez la famille Virtex-!! Pro de Xilinx, ce processeur peut

être un coeur hard (AS!C, cas du PPC405) immergé en dur dans le

FPGA ou un coeur soft (cas du Microblaze) instancié dans le

FPGA.

2 Vue imagée de la plateforme

auto-reconfigurable

charger en mémoire embarquée la version ASCII

(format RBT) des bitstreams générés, et de reconfigurer

dynamiquement et à la demande le(s) module(s) reconfigurable(s) du FPGA

via le port ICAP. Il est à préciser qu'après chargement en

mémoire embarquée, la plateforme devient autonome ; le temps de

reconfiguration d'un module n'inclut pas le temps de transfert de son bitstream

de l'ordinateur PC vers la mémoire embarquée.

A l'issue de ce stage, si le flot de mise en oeuvre de

l'auto-reconfiguration dynamique du Virtex-II Pro est parfaitement

maîtrisé, il peut servir au développement d'un OS temps

réels permettant de gérer la ressource FPGA, et ainsi

d'évaluer l'intérêt de la reconfiguration partielle et

dynamique.

Nous avons choisi le FPGA Xilinx Virtex II-Pro pour cette mise

en oeuvre car d'une part il est partiellement reconfigurable, et d'autre part

il intègre en dur un ou plusieurs coeurs de processeur PowerPC405.

1.3 Travaux similaires

La mise en oeuvre de la reconfiguration partielle et dynamique

sur FPGA Xilinx suivant un flot de conception modulaire (Modular Design

Flow) fait l'objet de beaucoup d'intérêt dans plusieurs

laboratoires de recherche universitaire actuellement. Pour la reconfiguration

partielle et dynamique, [12] et [20] présentent chacun des exemples

simples et très utiles. [6] montre un exemple appliqué à

la radio-logicielle (software radio). [8] et [15] détaillent la

méthodologie de mise en oeuvre. Mais dans les cas cités

precedemment, la reconfiguration est contrôlée depuis l'exterieur

; il ne s'agit donc pas d'auto-reconfiguration. [3] et [5] présentent

effectivement un cas d'auto-reconfiguration où le processeur PPC405

intégré reconfigure partiellement le FPGA. Mais dans le premier,

le contrôle de l'ICAP1 est totalement effectué par le

processeur , et non par un contrôleur instancié dans le FPGA. Dans

le second, on utilise l'outil JBits pour manipuler les bitstreams de

reconfiguration.

1.4 Environnement de travail

Ce stage s'est déroulé au sein du laboratoire

ETIS (Equipe Traitement des Images et du Signal) et plus

précisément dans l'équipe « Architecture ».

L'ETIS est abritée au sein de l'ENSEA (Ecole Nationale Supérieure

de l'Electronique et de ses Applications), et ses membres assurent outre la

recherche, des activités d'enseignement dans les deux

établissements d'attache du laboratoire que sont l'Université

Cergy-Pontoise et l'ENSEA. Les outils support mis à disposition par le

laboratoire pour ce stage sont essentiellement la carte de

développement Virtex-II Pro conçue par Memec Design

et les outils de développement ISE 7.1i et EDK 7.1.i de Xilinx.

1.5 Plan du rapport

Dans une première partie nous présenterons

sommairement le composant FPGA, et ensuite la notion d'architecture

reconfigurable de type FPGA et de leur intérêt. Ensuite nous

étudierons la méthodologie de mise en oeuvre de la

reconfiguration dynamique du Virtex-II Pro en nous focalisant sur le «

Modular Design Flow ». Enfin nous présenterons la plateforme

auto reconfigurable que nous avons mise en oeuvre, et qui permet au processeur

PPC05 intégré de reconfigurer dynamiquement et à la

demande une partie du FPGA. Quelques annexes en fin de document

présentent les differents codes en C et en vhdl développés

dans le cadre de ce projet ainsi que les détails sur l'utilisation de la

plateforme de démonstration que nous avons mis en oeuvre.

1 ICAP : Internal Configuration Access Port, port de

configuration interne des FPGA Xiinx

2. FPGA, RECONFIGURATION DYNAMIQUE ET CONCEPTION DES

SYSTEMES EMBARQUES

2.0 Introduction

Une architecture reconfigurable est une architecture dont les

ressources (calcul, interconnexions, ...) peuvent être modifiées

pour s'adapter à un traitement. Les FPGAs sont la parfaite illustration

de la reconfigurabilite matérielle au niveau bit d'une architecture. Ces

dernières années sont apparus des FPGAs reconfigurables

dynamiquement et/ou autoreconfigurables. Aujourd'hui, la plupart des

architectures ont un certain degré de reconfigurabilité.

La reconfiguration dynamique implique que le FPGA peut

être partiellement reconfiguré sans perturber le fonctionnement

continu du reste du composant qui n'a pas été reconfiguré.

L'autoreconfiguration est une forme de reconfiguration dynamique. En effet,

elle suppose l'implémentation du contrôle de la reconfiguration

partielle du FPGA sur une partie de ses propres ressources. Ceci n'est possible

que si l'intégrité de la logique de contrôle

implémentée dans le FPGA est assurée durant la

reconfiguration.

Par ailleurs, la croissance continue de la densité

d'intégration des puces électroniques permet de concevoir

aujourd'hui des systèmes électroniques entiers sur une seule

puce. Cette avancée technologique profite au premier chef aux FPGAs qui

en outre ont des fréquences de fonctionnement de plus en plus

élévées, des consommations et des temps de reconfiguration

en baisse constante. Tous ces atouts font aujourd'hui des FPGAs de serieux

concurrents aux solutions « tout ASIC », avec la flexibilté en

plus.

On parle de plus en plus de conception à base de FPGAs,

d'où les acronymes SOPC (SystemOn-a-Programmable-Chip) et rSOC

(reconfigurable-SOC) ; ceci implique clairement que l'utilisation des FPGAs ne

se limite plus comme à ses débuts, au prototypage rapide des

circuits ASICs.

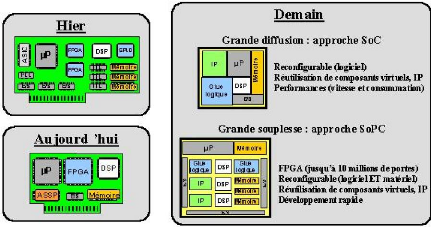

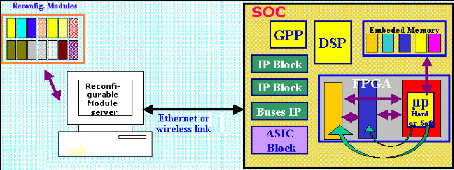

La Figure 1 montre les deux approches qui

prédomineront dans la conceptions des systèmes numériques

sur une seule puce. L'approche SOC (System-On-a-Chip) qui consiste

à intégrer sur une seule puce ASIC des composants

hétérogènes, et l'approche SOPC

(System-On-aProgrammable-Chip) qui consiste à implémenter

presque tout le système entier sur une seule puce programmable de type

FPGA. La première approche permet une plus grande diffusion, alors que

la seconde apporte beaucoup plus de souplesse. La tendance aujourd'hui est

davantage à la conception des circuits FPGAs intégrant des coeurs

de processeurs (hard ou

soft) et autres blocs ASICs dediés au traitement

numérique du signal (additionneurs, multiplieurs, Ram, etc...) et aux

communications (I/Os).

Il est a noter également que le flot de conception des

FPGAs s'est essentiellement appuyé sur celui largement eprouvé

des ASICs.

Figure 1 : Exemple de Systèmes Embarqués

[9]

Figure 2 : Evolution des systèmes électroniques

[17]

Dans ce chapitre, nous présenterons la notion

d'implémentation matérielle et/ou logicielle d'une application,

puis le composant FPGA en nous focalisant sur le Virtex-II Pro, ensuite

l'intérêt des architectures reconfigurables et les differents

scénarii de reconfiguration.

2.1 Implémentation logicielle vs

implémentation matérielle d'une application

2.1.1 Implémentation logicielle (Figure 3.a)

Dans un modèle d'exécution logicielle, le

traitement est séquentiel et exécuté par un processeur. En

effet, un CPU (Central Processing Unit) exécute une tâche (ou une

operation) à la fois. Toute application est découpée en

tâches unitaires exécutées les unes à la suite de

autres (Figure 3.a). Le passage d'une tâche à l'autre

nécessite une sauvegarde de contexte (context switch) qui permet de

conserver la cohérence globale de l'application, et donner une apparence

d'exécution parallèle des tâches. Mais ce modèle

nécessite des processeurs de plus en plus rapides pour répondre

à la complexité algorithmique des applications. Or les

fréquences de fonctionnement des processeurs ne sauraient être

augmentées indéfiniment a cause d'une part des limites

technologiques, et d'autre part d'une augmentation de la consommation qui n'est

pas souhaitable dans les systèmes embarqués.

Figure 3 : Implémentation temporelle vs

implémentation spatiale [13]

2.1.2 Implémentation matérielle (Figure

3.b)

Par contre dans un ASIC ou un FPGA, les applications

(algorithmes, fonctions, etc...) décrites dans un langage de description

de circuits (VHDL, Verilog, etc...) sont implémentées

matériellement; ceci apporte un gain de performance supérieur

à celui des processeurs grâce à l'implémentation

spatiale (parallèlisme) des tâches [13]. En effet dans ce type

d'implémentation matérielle, seul le temps de propagation des

signaux de l'entrée à la sortie d'un système fixe sa

limite supérieure en fréquence.

En outre, la reconfigurabilité dynamique de

certains FPGAs permet de faire évoluer l'architecture pour s'adapter au

traitement (Figure 3.c), contrairement aux ASICs. Il est aujourd'hui

envisagéable d'implémenter et d'exécuter

séquentiellement sur ce type de composants reconfigurables plusieurs

algorithmes, et de profiter à la fois de leur reconfigurabilité

(flexibilité) et de leur performance. Pour cela une architecture

reconfigurable inclut généralement deux principales parties, une

partie matérielle et une partie logicielle. La partie logicielle

comprend généralement un processeur (à usage

générique - GPP ou orienté traitement du signal -

DSP) chargé du contrôle et de la gestion de la

reconfiguration de la partie

matérielle, ainsi que de l'exécution des

tâches encore dévolues au logiciel. Elle utilise la partie

matérielle (un ou plusieurs FPGAs) comme accélérateur

matériel, en y implémentant les parties les plus critiques des

traitements.

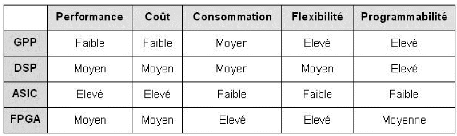

Le tableau comparatif ci-dessous (Table 1) permet de

situer les FPGAs parmi les principaux types d'architectures et leurs

caractéristiques [6].

Table 1 : Comparatif des caractéristiques de

différentes implémentations [6]

2.1.3 Partitionnement Matériel / Logiciel

Les problèmes de partitionnement

matériel/logiciel des tâches apparaissent dès que les

ressources permettent une implémentation matérielle et/ou

logicielle des tâches. En effet, pour les systèmes incluant une

architecture matérielle reconfigurable et un ou plusieurs processeurs(

GPP, DSP), le programme doit être prémièrement

partitionné en sections devant s'exécuter soit logiciellement,

soit matériellement. En général, les opérations

récursives et de contrôle sont plus efficaces sur processeur. Mais

les outils disponibles à ce jour fournissent en général

soit le modèle matériel, soit le modèle logiciel

d'implémentation d'une application. Des travaux sur des compilateurs

permettant d'automatiser ce processus de partitionnement existent1

[10]. Mais avec le developpement d'architectures reconfigurables, il est de

plus en plus envisagé d'avoir des tâches ayant les deux

modèles d'exécution, l'un où l'autre étant

utilisé à un instant donné suivant des critères

d'efficacité et de priorité par exemple.

Notre étude étant essentiellement circonscrite

à la mise en oeuvre d'une plate-forme auto-reconfigurable dynamiquement

sur FPGA Virtex-II Pro de Xilinx, nous présentons suscintement

ci-dessous l'architecture des FPGAs ainsi que les différents

scénarii de reconfiguration, puis nous relèvons ceux qui sont

envisagéables sur cette famille de FPGAs.

1 C'est le cas du projet POLIS qui a mis au point un outil

du meme nom, permettant la conception conjointe matériel/Logiciel

(CoDesign) et supportant des outils de spécification niveau system comme

Esterel. Universite de California Bekerley,

http://embedded.eecs.berkeley.edu/Respep/Research.

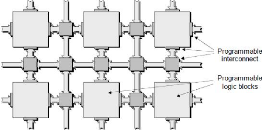

2.2 Architecture des FPGAs

2.2.1 Introduction

C'est une famille de puces électroniques introduite par

la société Xilinx. Les FPGAs sont les premières

architectures reconfigurables à avoir été

proposées. Ils ont l'avantage d'être recongurables à

souhait. Ils comprennent des blocs configurables qui permettent de

générer des fonctions logiques combinatoires ou

séquentielles sur 1 bit. Ainsi, en associant plusieurs

éléments configurables de 1 bit par le biais d'interconnexions

tout aussi programmables (Figure 4), l'utilisateur est capable de

générer n'importe quelle fonction logique.

Si le nombre d'unités configurables est suffisamment

important, il est possible, en associant ces blocs, de recréer un

système entier. C'est pour cette raison que ces composants sont

utilisés pour faire des prototypes de circuits, avant de les envoyer

chez le fondeur de silicium. Son développement s'est

accéléré sous la double pression du

«Time-To-Market»1 et de

«FirstTime-Right»2 (minimiser d'une part le temps

de développement et de mise sur le marche des circuits digitaux et

d'autre part éviter toute défaillance dans leur conception).

2.2.2 Principe de fonctionnement et Architecture Interne

des FPGAs

La structure interne ainsi que la technologie utilisées

dans les FPGAs varient suivant les fabricants. Mais la structure globale de la

Figure 4 (si on y rajoute les entrées/sorties programmables)

est valable indépendamment des fabricants. En général le

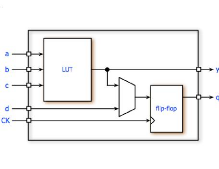

bloc configurable est bati autour d'un LUT (Look-Up-Table, voir Figure

5). Un LUT permet d'implémenter toute fonction combinatoire (ou

séquentielle, d'où le flip-flop de sortie) à quatre

entrées.

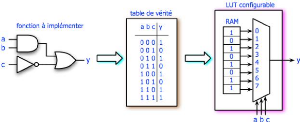

La Figure 6 présente l'implémentation

d'une fonction combinatoire a l'aide d'une LUT. La table de vérite de la

fonction est stockée dans une RAM connectée à un

multiplexeur. Configurer une LUT revient donc à stocker la table de

vérite de la fonction dans sa RAM et à router les signaux a, b et

c vers les entrées de sélection du multiplexeur.

1 Le Time-To-Market qui traduit donne «temps de mise

sur le marché» est vrai challenge pour reduire le temps de

developpement d'un nouveau produit électronique afin de s'adapter a la

reduction croissante du cycle de vie de produits électroniques grands

publics.

2 Le First-Time-Right par contre traduit la

nécessité d'éviter toute erreur dans la conception d'un

circuit avant l'envoi chez le fondeur d'ASIC; en effet un ASIC

défectueux coute en NRE (Non Recurring Engineering), cette somme que les

fournisseurs d'ASIC facturent au concepteur des le démarrage de

processus de fabrication. Dans tous les cas, le cout de la technologie ASIC

contribue largement a l'émergence des FPGAs.

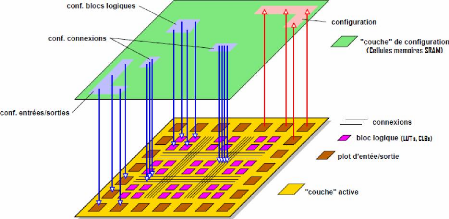

Figure 4 : Structure globale des FPGAs [14]

Figure 5 :

Un LUT (Look-Up-Table) [14]

Figure 6: Implémentation d'une fonction Y = ab +

(non)C [14]

Grâce à sa granularité fine, on est

capable avec un circuit FPGA d'exploiter le parallélisme autant qu'avec

un circuit spécifique ASIC dans la mesure où l'on est capable de

le recréer entièrement par association des éléments

configurables. Mais cette fine granularité qui offre toute la

flexibilité logique voulue est au prix d'une performance moindre

comparée aux ASICs. En effet, elle apporte deux problèmes :

- La baisse de la fréquence de fonctionnement due au temps

de propagation des signaux.

- L'augmentation des temps de reconfiguration requis, ce qui

peut empêcher par exemple d'enchaîner sur le même circuit

deux configurations pour des applications à contraintes temps

réel [2].

Grâce aux avancées technologiques, les FPGAs sont

envisagés aujourd'hui (sur les plans du coût et des performances)

comme une alternative entre les solutions dédiées très

performantes (ASIC) et les solutions programmables très flexibles

(processeurs et DSP). Les principaux fabricants proposent aujourd'hui des FPGAs

intégrant jusqu'à 10 millions de portes logiques, et sur lesquels

on peut même synthétiser un coeur de microprocesseur (Microblaze

sur FPGAs Xilinx [21], Nios sur ceux d'Altera). De même, les FPGAs

à mémoire de configuration de type SRAM1 permettent la

reconfiguration dynamique. C'est le cas du Virtex-II Pro.

2.2.3 Exemple d'architecture de FPGA : la série

Virtex-II Pro de Xilinx (figure10)

Introduite en 2002 et fabriquées en technologie CMOS

1.5V/130nm, la série Virtex-II Pro vise les fortes densités

(jusqu'à 10 millions de portes). Elle intègre en dur de un

à quatre coeurs de processeur RISC IBM PowerPC 405 (jusqu'à

400Mhz) ainsi que des blocs optimisés pour les applications

orientées traitement du signal (blocs de RAMs de 18 Ko et de

multiplieurs 18x18, etc...). Outre la logique programmable, elle comprend ainsi

(Error! Reference source not found.):

- Des entrées/sorties configurables en

entrée, sortie ou bidirectionnel, supportant de nombreux standards

(LDVS, PCI-X, differentiel,...) et interfaçant les pins externes du

circuit et la logique reconfigurable interne.

- Des blocs multiplieurs 18x18 bits cablées et

donc rapides et de faible consommation.

- Des CLBs (Configurables Logics Blocs - Figure

7) qui sont des blocs de ressources programmables permettant

d'implémenter des fonctions combinatoires et séquentielles.

- Des émetteurs/récepteurs série haut

débit (RocketIO) supportant des débits atteignant 3,125 Gb/s

par canal (6,25 Gb/s pour les RocketIO X).

- Des blocs de mémoire selectRAM qui sont des

RAM dual port de 18 kb, chacune programmable en mémoire de 16K X 1 bit

à 512 x 36 bits, et cascadables pour former des blocs mémoires de

taille plus grande.

- Des blocs DCMs (Digital Clock Manager) permettant

la synthèse de fréquences (multiplication et divivion d'horloge),

l'auto-calibration, la compensation des retards pour une parfaite distribution

d'horloge, etc...

1 On peut distinguer les FPGAs par leur type de

mémoire de configuration (fuse, anti-fuse, EEPROM, E2PROM/Flash, SRAM).

Le type détermine la reconfigurabilité du FPGA. Par exemple les

FPGAs à SRAM peuvent facilement être reconfigurés

partiellement et dynamiquement.

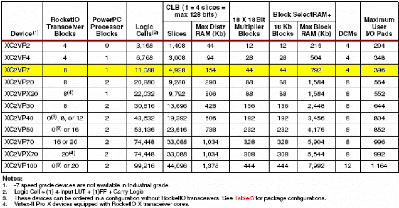

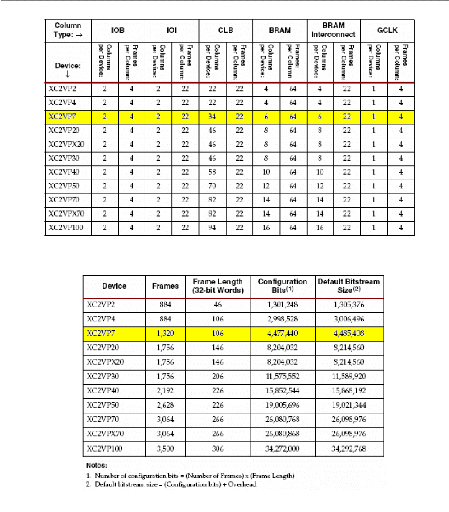

Table 2 : FPGAs de la famille Virtex-II Pro et leurs

principales ressources

(la colonne grisée montre les éléments

du FPGA XVP7 que nous avons utilisée)

2.2.4 Détails de quelques unes des ressources du

Virtex-II Pro

Nous détaillons ci-dessous les caractéristiques qui

permettent de mieux comprendre les règles de reconfiguration du

Virtex-II Pro.

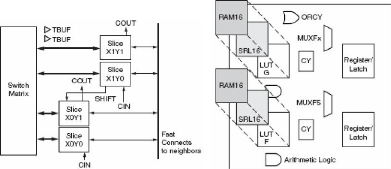

a) Les CLBs (Configurable Logic Blocks - Blocs de

logiques configurables)

Un FPGA Xilinx comprend un certain nombre de colonnes de

CLBs. Chaque CLB comprend 4 Slices identiques et 2 buffers tri-states (TBUF,

Figure 7) . Chaque colonne de CLB comprend 2 colonnes de Slices.

Chaque CLB est relié à une matrice d'interconnexion (switch

matrix) pour accéder à la matrice générale de

routage. Les Slices d'un même CLB sont reliés entre eux et aux

CLBs voisins par des interconnexions directes et rapides (fast connects to

neighbors, Figure 7).

b) Les SLICES (Figure

78) Chaque Slice contient :

- Deux générateurs de fonction (F & G); ce

sont des LUTs (Look-Up-Table) pouvant implémenter soit une fonction

logique à 4 entrées, soit une mémoire SelectRAM 16 bits

(dans ce cas on parle de distributed selectRam) , ou encore un

registre à décalage 16 bits.

- Deux éléments de stockage (Register/Latch) qui

servent de registres D flip-flop de sortie.

- Deux multiplexeurs MUXFX qui combinés aux

générateurs de fonction permettent de générer des

fonctions logiques de plus de 4 entrées.

- Des portes logiques qui facilitent l'implémentation de

la logique arithmétique ( des XORs pour additionneurs, des ORs pour les

sommes de produit et des ANDs pour les multiplieurs).

- Des chaînes de propagation rapide de retenue (CY).

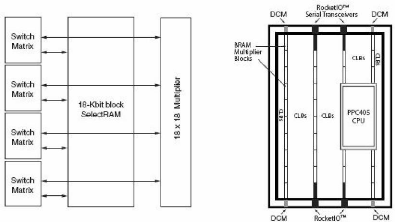

Figure 7 : Structure interne d'un CLB Figure 8 : Structure

interne d'un Slice

Figure 9 : Bloc multiplieur et SelectRam Figure 10 : Vue

générale du

Virtex-II Pro XVP7

c) Les blocs multiplieurs 18 x 18 bits

(Figure 910)

Ils réalisent des multiplications en complement

à 2 (signes), et peuvent être associés à de blocs

memoires SelectRam 18 Kb pour former des modules MAC (Multiplier-Accumulator)

très utiles en traitement numérique du signal (filtres FIR et

IIF). Cables en dur, ils sont optimisés en vitesse et en consommation.

Un virtex-II pro peut contenir jusqu'a 444 blocs multiplieurs de ce type, et

autant de blocs SelectRam (Error! Reference source not

found.).

Toutes ces ressources permettent également au Slice de

combiner avec des Slices voisins pour implémenter des fonctions plus

complexes.

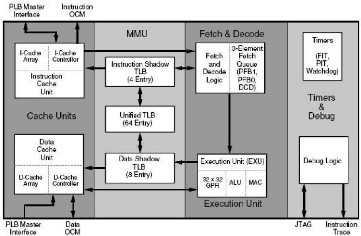

d) Le processeur PowerPC 405

Le PowerPC 405 est un processeur RISC1 de 32 bits

d'architecure Harvard1. Il est optimise pour de hautes performances

(jusqu'à 400Mhz pour certains) et des basses consommations (0.9mW/MHz).

Il est intégré dans le FPGA Virtex-II Pro comme le montre la

Figure 9 10.

Figure 11 : Architecture générale du processeur

PowerPC 405 Il possède essentiellement:

- Une MMU (memory management unit) qui peut faciliter la misen

en oeuvre d'un systeme de fichier, solution envisageable dans notre cas pour

stocker les configurations en mémoire embarquée sous forme de

fichier.

- Deux interfaces mémoires (Figure 11) ;

l'interface OCM (On-Chip-Memory) subdivisée en deux blocs ; l'un pour

les données et l'autre pour les instructions et l'interface PLB.

- Une interface JTAG permettant le debugage (en plus de trois

autres modes de debogage supportés).

- Un pipeline de 5 étages

- Des caches de données et d'instruction

séparées et de 16 Ko chaque. - 3 Timers programmables.

1 Reduced Instruction Set Computer ; concept consistant

à réduire le jeu d'instruction des processeur, et parti du

constat suivant lequel dans 80% des cas un processeur n'utilisait que 20% de

son jeu d'instruction (essentiellement des Load/Sore)

- Une unité de division/multiplication.

En outre ce processeur implémenté en dur occupe

2% de la surface totale d'un FPGA Virtex-II Pro XVP50 par exemple

(Error! Reference source not found.). Mais il n'a pas

d'unité arithmétique flottante.

Le processeur est connecté au bus PLB (Processor Local

Bus) directement, et a un second bus (OPB pour On-chip Peripheral Bus)

via un pont entre les deux bus.

2.3 Les divers scénarii de reconfiguration des

FPGAs

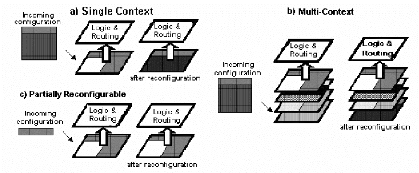

2.3.1 Les modèles de reconfiguration [4]

Un facteur de différenciation des FPGAs est leurs modes

(ou possibilités) de

configurations qui varient d'une famille à l'autre. Ces

modes sont souvent liés à la technologie de fabrication et

peuvent être des critères déterminants lors du choix du

FPGA cible pour implémenter une application. Par exemple pour une

application nécessitant plusieurs configurations (contextes), il peut

être profitable d'utiliser un FPGA reconfigurable dynamiquement

(RTR-Runtime Reconfigurable). Comme décrit dans [4], on peut

classifier les architectures reconfigurables en trois catégories suivant

leurs modèles de reconfiguration (Figure 12). Ces

modèles qui s'appliquent également aux FPGAs sont:

a) La reconfiguration à contexte unique

(Single Context)

Elle est encore appelée Reconfiguration totale car la

reconfiguration se fait entièrement sur toute la surface de la matrice

de configuration (sur tout le FPGA par exemple). Tous les bits de la matrice de

configuration sont donc réécrits, même s'ils n'ont pas

changé entre deux configurations (Figure 12.a). Ce qui est

évidemment une perte de temps. La reconfiguration à contexte

unique est utilisée pour des applications statiquement

reconfigurables (SRD - Statically Reconfigurable Design). Plusieurs

applications sont programmées une à la fois (par chargement du

fichier binaire correspondant) sur le FPGA; un Reset du FPGA est

effectué entre deux programmations.

b) La reconfiguration multi-contextes

(Multi-Context)

Elle se fait sur des FPGAs ayant plusieurs mémoires de

configuration se trouvant sur des plans différents (Figure

12.b). On peut ainsi "charger" plusieurs plans de configurations dans le

FPGA, et le passage d'une configuration à l'autre (commutation de

contexte) se fait par commutation d'un plan mémoire à un autre.

Par rapport à la reconfiguration à contexte unique,

1 Memoires de données et des programmes

separées et accessibles par des bus séparés

également, ce quipermet l'accès simultanée des

données et des programmes, contrairement a l'architecture de Von

Neumann. Ceci

le temps de reconfiguration en est fortement

accéléré. En outre, une mémoire inactive peut

être reprogrammé pendant que l'autre est active sur le FPGA. Une

sorte de mémoire cache de contexte existe alors dans le FPGA.

Ce type de reconfiguration s'apparente au Page Mode

[1] dans les séries Stratix et APEX 20K d'Altera où on peut

charger jusqu'à 8 configurations en mémoire Flash et passer

dynamiquement d'une à l'autre. Dans ce cas la mémoire Flash est

divisée en pages, chaque page contenant un bitstream1 total

pouvant configurer tout le FPGA ; il ne s'agit pas de plan de configuration, et

donc pas d'accélération de temps de reconfiguration.

Figure 12 : Les différents types de reconfiguration

[4]

c) La reconfiguration partielle ( Partially

Reconfigurable)

Contrairement à la reconfiguration à contexte

unique ou multi-contextes, on peut configurer partiellement le FPGA afin de

n'utiliser que les ressources nécessaires à

l'implémentation de l'application (Figure 12.c) ; on reduit

ainsi la consommation en énergie et en ressources logiques du FPGA,

ainsi que le temps de reconfiguration.

En outre, une portion du FPGA peut être

reconfigurée dynamiquement (c'est-à-dire reconfigurer une partie

du FPGA pendant que l'autre active), ce qui cache la latence due à la

reconfiguration qui peut s'observer dans la reconfiguration à contexte

unique ou multiple. Reconfigurer dynamiquement permet l'implémentation

matérielle de beaucoup plus de sections de l'application et

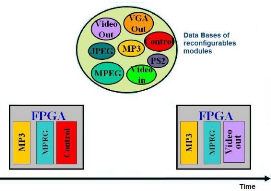

d'accélerer ainsi l'exécution. Par exemple sur la Figure

13, le module «Control » est remplacé par le

module « Video out » par reconfiguration partielle du

FPGA.

accelère l'execution et est tres utilisé dans

les processeur de type DSP

1 Fichier de flot de données contenant une

configuration prête à être chargée dans le FPGA. Dans

le cas du Virtex, il peut être en .bit pour le binaire ou en .rbt pour

son equivalent ASCII. L'Outil de programmation de FPGA (Impact par exemple)

supporte indifféremment l'un ou l'autre type de fichier pour la

reconfiguration.

Figure 13 Reconfiguration partielle et dynamique du

FPGA

2.3.2 Configuration du Virtex-II Pro de Xilinx

a) Vue en couche d'un FPGA

Le FPGA peut être vu comme une structure à deux

couches (Figure 14):

Figure 14 : Vue en couche d'un FPGA [16]

- Une couche active ou couche logique qui comprend des ressources

logiques, des

entrées/sorties, des ressources de routage, et

éventuellement des blocs dediés.

- Une couche de configuration encore appelée

mémoire de configuration et permettant de

programmer électriquement les caractéristiques

des ressources de la couche active. En effet,

toutes les ressources logiques

du FPGA sont contrôlées par le contenu de la

«mémoire de

configuration» (chez Xilinx cette mémoire

est à base de cellules SRAM1 volatiles, le FPGA doit donc

être reconfiguré à chaque mise sous tension). Leur contenu

fixe l'équation des LUTs, le routage des signaux, les

entrées/sorties et leur tension ainsi que les paramètres de

toutes les autres ressources du FPGA.

Pour programmer un FPGA, les instructions de contrôle de

configuration ainsi que les données à écrire en

mémoire de configuration sont fournies sous forme d'un bitstream qui est

envoyé dans la puce via une interface de configuration (JTAG, SelectMap,

Série,...).

b) Organisation de la mémoire de configuration

et son influence sur la délimitation des modules

reconfigurables

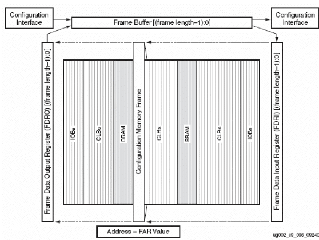

La mémoire de configuration du Virtex-II Pro

est constituée d'un certain nombre de colonnes

élémentaires de mémoires appelées Frames.

Une Frame est la plus petite unité de mémoire

reconfigurable individuellement dans un Virtex-II Pro ; elle est donc

adressable individuellement sur 32 bits et permet ainsi aux FPGAs Xilinx

d'être partiellement reconfigurables2. Une Frame occupe toute

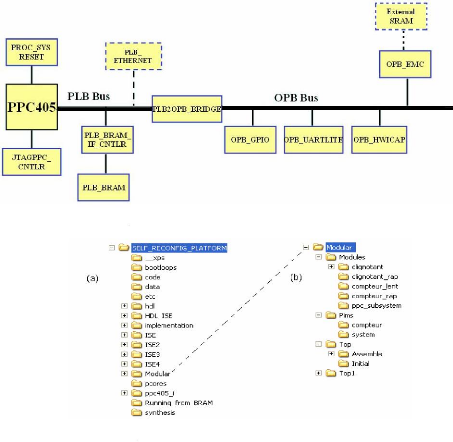

la hauteur du FPGA et chaque ressource programmable (CLBs, IOBs, IOIs, GCLKs,

BRAMs) est constituée d'un certain nombre de frames (Error!

Reference source not found.). Le nombre de Frames par ressource ainsi

que la taille de la Frame dépendent

du type de FPGA et fixent la taille du fichier de

configuration totale (Error! Reference source not found.). Par

exemple dans un Virtex-II Pro XVP7 constitué de 1320 frames, on trouve

34 colonnes de CLBs, chacune comprenant 22 frames. A l'aide de la table 3, on

peut refaire le calcul de ce nombre total de frames dans un Virtex-II Pro XVP7

comme suit :

Nbre_Frames_XVP7 = 2x4 IOB_frames + 2x22 IOI_frames + 34x22

CLB_frame

+ 6x64 BRAM_frames + 6x22 BRAMi_frames + 1x4 GCLK_frames =

1320 frames.

Reconfigurer partiellement un FPGA comme le Virtex-II Pro de

Xilinx [24] consiste en la reconfiguration d'une ou plusieurs colonnes (plus

précisement des Frames) de la mémoire de configuration.

L'alignement en colonne des frames (et donc des ressources) sur la surface

physique du FPGA explique le fait que, dans la reconfiguration partielle, on

attribue exclusivement à un module les I/Os en contact avec la zone du

FPGA attribuée au module. En effet, un module situé à

l'extrémité gauche du FPGA engloberait forcément la

première colonne d'entrées/sorties IOBs (figure 16) et serait

ainsi le seul pouvant utiliser les entrées/sorties du côté

gauche du FPGA.

1 Il est à noter qu'il existe plusieurs technologies

de fabrication des FPGAs, et elles se distinguent généralement

par le type de mémoire de configuration utilisé (SRAM, fuse et

anti-fuse, etc...).

2 La société Atmel propose aussi des FPGAs

à reconfiguration partielle, les AT40K, utilisant un système de

mémoire cache de contextes de configuration très

intéressant pour des applications de notre type.

Table 3 :Répartition des ressources en frames dans les

FPGAs Virtex-II Pro

Table 4 : Taille des données de configuration dans la

série Virtex-II pro

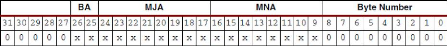

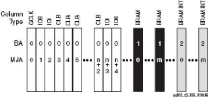

La Figure 15 montre le format d'une adresse de Frame

et la Figure 16 montre le principe d'adressage des Frames. Par

exemple, toutes les adresses ou le mot binaire BA1 = 00 adressent

les colonnes de Frames configurant les GCLK, les IOB, les IOI et toutes les

colonnes

1 Chaque frame de configuration a une adresse unique sur 32

bits composee des champs BA (Block Address), MJA (Major Address) et MNA (Minor

Address) et un octet. Comme indique a la figure 16. BA indexe le bloc de

ressources a configurer (par exemple les blocs BRAM), MJA identifie la colonne

dans le bloc, MNA identifie la frame et l'octet sert de compteur de mots par

frame. Un mot dans une frame ne pourrait etre adresse, voir [Xilinx 06] page

339 pour details.

de CLB alors que pour BA = 01 (resp. 10 ou 2 en decimal) on

adresse les colonnes frames configurant les colonnes BRAM (resp. colonnes de

BRAM INTerconnection). La valeur des bits MJA et MNA permet d'adresser une

frame précise.

Dans un design modulaire, la largeur minimale admissible d'un

module est de 4 Slices (plus précisément 4 colonnes de Slices

correspondant à 2 colonnes de CLBs, car la hauteur d'un module est

toujours égale à celle du FPGA). Reconfigurer partiellement un

module revient à reconfigurer toutes les frames de ses ressources.

Figure 15 : Format d'adresse d'une Frame

Figure 16 : Adressage de la mémoire de

configuration

c) Les modes de reconfiguration

La configuration des FPGAs Xilinx peut être

effectuée de l'extérieur (à partir d'un PC par exemple, ou

d'un microcontroleur) selon les modes suivants :

- Serial (Programmation série).

- JTAG / Boundary-Scan (Programmation via la sonde JTAG). -

SelectMap1 (Programmation parallèle).

Et de l'intérieur par:

- Le port ICAP qui est une interface permettant

d'accéder à la mémoire de configuration du FPGA. Cette

interface est celle que nous avons utilisée pour la reconfiguration

partielle du FPGA par le processeur PPC 405 intégré, mais avant,

le FPGA doit avoir été configuré totalement par l'un des

modes de reconfiguration extérieur cité ci-dessus.

1 SelectMap est une interface de configuration du FPGA depuis

l'exterieur. Il permet d'accéder en lecture/écriture à la

mémoire de configuration du FPGA suivant plusieurs modes. Pour les

détails, voir [Xilinx 06] en page 306.

d) Le port de configuration interne

ICAP

Le port ICAP (Figure 17) est un sous-ensemble de l'interface

SelectMap. Il est physiquement présent sur le FPGA en bas a

l'extrême droite de la puce. Il utilise le même protocole que

SelectMap en mode esclave. Il est capital dans la mise en oeuvre de

l'autoreconfiguration. En effet, il sert d'interface d'accès interne

à toute la mémoire de configuration du FPGA et permet ainsi au

processeur intégré de le reconfigurer partiellement. Dans [24] en

page 317 sont précisées les précautions à prendre

vis-a-vis des autres modes de configuration lors de l'utilisation du port

ICAP.

Figure 17 : Port ICAP Figure 18: Architecture materielle

pour

la reconfiguration via le port ICAP

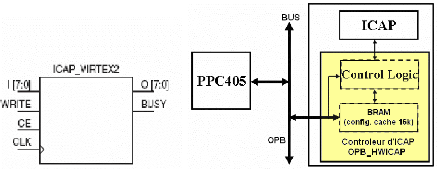

Pour faciliter l'utilisation de l'ICAP, Xilinx fournit sous

forme d' IP1 un Controleur d'ICAP2 (Figure

178) dont les détails peuvent être trouvés dans [25].

Le contrôleur est instancié comme périphérique du

processeur PPC405 et implemente sous EDK à l'aide des ressources du

FPGA. Il est connecté au bus OPB (On chip Peripheral Bus). Il utilise

une BRAM de 16 Ko (suffisant pour contenir les données de configuration

d'une Frame) qui sert de mémoire de cache aux données de

configuration en provenance du bus pour le port ICAP (reconfiguration) ou vice

versa (Readback) . La BRAM double port est connecté d'un coté au

contrôleur d'ICAP et de l'autre au bus OPB.

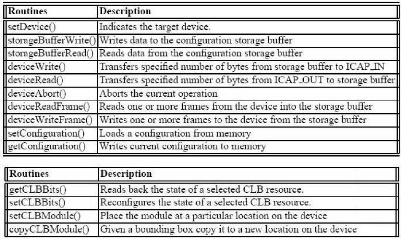

Xilinx fournit également pour le contrôleur une

couche logicielle (pilotes) sous forme de fonctions légères

écrites en C (Error! Reference source not found.) et

évitant d'avoir à gérer la communication entre le bus et

l' ICAP. Par exemple l'écriture en mémoire de configuration du

FPGA se fait en 2 temps (voir table 5):

1 Intellectual Property

2 Sur la figure 17, opb_hwicap est le nom d'instance

choisi pour le contrôleur d'ICAP lors de son implémentation sous

EDK comme périphérique du processeur. De même on le

connecte à un bus (OPB) et on lui attribue une adresse d'implantation

dans l'espace d'adressage du bus.

- La fonction storageBufferWrite( ) permet au

processeur d'écrire un certain nombre de trames binaires (512 mots de 32

bits au maximum pour les 16Ko de BRAM) en BRAM de cache.

- La fonction deviceWriteFrame( ) permet ensuite au

contrôleur de transférer ces trames précédemment

écrites en BRAM vers le port ICAP qui les interprètent pour

configurer le FPGA frame par frame. Ces trames proviennent des bitstreams de

configuration partielle du FPGA et contiennent toutes les informations

nécessaires à l'adressage et à la configuration d'une ou

plusieurs frames.

Les fonctions storageBufferRead( ) et

deviceReadFrame( ) jouent respectivement le même rôle que

les deux précédentes mais plûtot dans le sens ICAP -

Processeur PPC405 et servent donc à lire le contenu des frames du FPGA

(Readback).

Table 5 : Fonctions permettant de lire et écrire en

mémoire de configuration via le port ICAP

Figure 19 :L' Interface de configuration du Virtex-II Pro et

ses registres

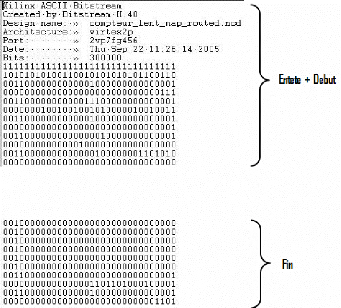

e) Analyse des trames de

configuration1

1 Premieres et les dernieres lignes d'un fichier bitstream au

format ASCII (.rbt)

Comme expliqué plus haut, configurer le FPGA revient

à y envoyer à l'interface de configuration (Figure 19)

un fichier bitstream de configuration sous forme de trames qui comprennent les

données de contrôle de configuration et les données

à écrire dans les frames de configuration pour programmer les

ressources. On distingue globalement:

- Les trames d'écriture

- Les trames de lecture

- Les trames de synchronisation

- Etc...

[23] étudie en détails au chapitre 4 toutes ces

trames et les registres cités dans l'exemple cidessous.

Les premières et les dernières lignes (il peut

en avoir plusieurs milliers de lignes suivant la taille du module) d'un exemple

de fichier bitsteam au format RBT apparaît plus haut. Il permet de

reconfigurer un module du FPGA. Ce sont donc des trames d'écriture. Nous

l'avons généré dans le cadre de ce projet. La trame de

reconfiguration commence en ligne 8. On peut décrypter ces quelques

lignes de trames comme suit [23] :

- Les 7 premières lignes représentent

l'entête du fichier RBT ; elles renferment quelques renseignements.

- 0xff, 0xff, 0xff, 0xff : Mot inutile (ligne 8).

- 0xaa, 0x99, 0x55, 0x66 : Mot de synchronisation. Demande au

FPGA de commencer à analyser les mots suivants.

- 0x30, 0x00, 0x80, 0x01 : Mot d'entête ; annonce une

écriture de 1 mot dans le registre de commandes.

- 0x00, 0x00, 0x00, 0x07 : Remise à zéro du

registre du CRC.

- 0x30, 0x01, 0xc0, 0x01 : Mot d'entête. Annonce

l'écriture du code d'identification du FPGA (registre IDCODE).

- 0x01, 0x24, 0xa0, 0x93 : Code d'identification du FPGA

- 0x30, 0x00, 0x80, 0x01 : Mot d'entête. Annonce une

écriture de 1 mot dans le registre de commande (registre CMD).

|

- 0x00,

|

0x00,

|

0x00,

|

0x01 : Initialise l'écriture des données de

configuration

|

|

- 0x30,

|

0x00,

|

0x20,

|

0x01 : Mot d'entête. Annonce l'écriture de

l'adresse de la colonne

|

élémentaire.

- 0x00, 0x48, 0x0c, 0x00 : Adresse de l'unité

élémentaire à reconfigurer (voir figure 15 et figure

16).

- 0x30, 0x00, 0x40, 0xd4 : Mot d'entête. Annonce

l'écriture de 212 mots de 16 bits de configuration. Nous indiquons ici

la taille de l'unité élémentaire spécifique

à chaque FPGA.

- En fin de fichier on a toujours la même séquence

de trames, et le mot de fin est 0x00, 0x00, 0x00, 0x0D.

3. METHODOLOGIE DE MISE EN OEUVRE DE L'AUTO

RECONFIGURATION PARTIELLE ET DYNAMIQUE SUR LE VIRTEX-II PRO

Ce chapitre se focalise sur la mise en oeuvre sur FPGAs Xilinx

Virtex-II Pro d'un système auto-reconfigurable partiellement et

dynamiquement à l'aide d'outils de conception électronique.

L'auto-reconfiguration vient de ce que le processeur immergé dans la

puce FPGA reconfigure partiellement celle-ci.

Pour la reconfiguration partielle, Xilinx propose dans [20] deux

méthodes:

· Le Small Bit Manipulation à l'aide l'outil

JBits1

· Le Modular Design Flow

Le Small Bit Manipulation permet de modifier

rapidement un ou plusieurs détails dans un design, comme par exemple la

modification d'un CLBs, IOBs, LUT ou Block RAM. Il est à noter que les

outils comme JBITs fournissent une interface et des classes Java permettant de

manipuler (lire et modifier) individuellement les données de

configuration de chaque ressource du FPGA.

Le Modular Design Flow est une approche

modulaire qui permettrait dans le cadre de la reconfiguration partielle, de

reconfigurer un module entier, et non pas un détail dans le module. Dans

le cadre de ce stage, nous avons utilisé cette approche qui est par

ailleurs suggérée par Xilinx pour la reconfiguration

partielle.

3.1 Méthodologie de Conception

Pour la conception des designs pour FPGAs Xilinx, il existe

deux démarches principales, une démarche dite standard

(Ordinary Design Flow) et une démarche dite incrémentale

(Incremental Design Flow). Après une brève description

de la première démarche, nous nous focaliserons sur la seconde et

plus particulièrement sur le Modular Design Flow, une

méthode incrémentale suggérée par Xilinx pour la

mise en oeuvre d'applications partiellement

1 JBits est une API (Application Programmable Interface) java

fournie par Xilinx et contenant un jeu de classes permettant de manipuler

(lire/modifier/ecrire) individuellement toutes les ressources reconfigurables

du Virtex. JBits permet de modifier dynamiquement le bitstream du Virtex. Par

exemple, il peut permettre d'extraire un bitstream partiel du bitstream total

d'un design fait suivant le modular design flow. Nous n'avons pas utilise JBits

dans le cadre de ce travail (auto-reconfiguration) car il n'est pas souhaitable

que le processeur PPC405 embarque puisse supporter JVM(Java Virtual

Machine).

reconfigurables et supportée par ses familles de FPGAs les

plus récentes (Spartan et Virtex). Ces méthodologies de

conception

permettent de dérouler tout le processus de la

description du design à la génération des fichiers de

configuration ; elles sont mises en oeuvre dans des environnements

(ISE1 et EDK2) intégrant plusieurs outils Xilinx

que nous décrirons plus loin.

3.1.1 Flot de conception standard (Ordinary Design

Flow)

Dans le flot de conception standard, tout le design est

décrit dans un langage de description de circuit (Vhdl, Verilog) comme

un tout unique, puis synthétisé, simulé, placé et

routé. Les étapes minimales du flot de conception d'un design

sont figure 20 ci-dessous :

1. La description du design soit dans un langage de description

(Vhdl, verilog, SystemC), soit grâce à un outil de saisie

graphique qui génère le code Vhdl correspondant.

2. La simulation en vue de vérifier le bon

comportement.

3. La synthèse

4. Le placement et routage pour un FPGA précis.

5. La génération du fichier binaire de

configuration (bitstream) qui sera chargé sur le FPGA cible.

En cas de modification d'une partie du design, les

étapes ci-dessus sont entièrement refaites pour tout le design,

ce qui rend le processus très long. De même, cette méthode

ne facilite pas le découpage modulaire du design en vue d'une

répartition des tâches entre les membres d'une équipe,

contrairement au Modular Design Flow.

Le flot standard est supporté par l'outil

intégré ISE qui déroule automatiquement tout le processus;

il en résulte un fichier binaire unique (.bit) contenant les

données de configuration totale du FPGA.

Dans le cas de la conception d'un SOC, l'outil

intégré EDK permet de développer l'application

destinée au processeur intégré (de l'écriture du

code à la génération de l'exécutable), de

générer tous ses supports de communication (bus, uart, jtag,

Ethernet...), et de produire un

1 ISE : Integrated Software Evironment, environnement de

developpement integré de Xilinx, permettant de dérouler

automatiquement le flot de conception pour les FPGAs Xilinx de la saisie du

schema (ou l'ecriture en vhdl) a la génération du bistream de

programmation du FPGA.

2 Embedded Development Kit, environnement de developpement du

sous-système à processeur et périphériques

associés pour FPGAs Xilinx.

fichier binaire unique comprenant les données de

configuration totale du FPGA et l'exécutable pour le processeur du

SOC.

Mais ce flot standard ne permet que la configuration totale du

FPGA, et ne peut donc être utilisé dans le cadre de la

reconfiguration partielle des FPGAs Xilinx.

|

Figure 20 : Flot de conception Standard pour les

FPGAs

|

|

3.1.2 Le Flot de conception incrémental

(Incremental Design Flow)

Contrairement à un flot de conception standard, un Flot

incrémental permet de découper le design en modules

séparément synthétisables. L'intérêt de cette

méthode est la possibilité de valider des modules du design bloc

par bloc. De même les modules conçus pour des designs

antérieurs peuvent facilement être réutilisés dans

de nouveaux designs sans plus être revalidés.

Les phases de Synthèse-Placement-Routage ne sont

ré-exécutées que sur les modules ayant été

modifiés, ce qui sollicite moins de puissance et de temps à

l'ordinateur hôte.

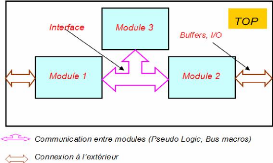

a) La synthèse

incrémentale (Figure 21)

Au lieu de synthétiser le design complet (Top, Figure

21), chaque module (Module 1,2,3 Figure 21) est

synthétisé séparément et son fichier netlist

généré (nom_entite.ngc).

Les modules sont déclarés comme des composants

dans le Top, puis instanciés et interconnectés (top.vhd,

annexe 4.1). Le niveau Top du design contient toute la logique globale, les

Entrées/Sorties (IOBs), les signaux, et les interconnexions

inter-modules. Tous ces éléments y sont déclarés et

instanciés. Les fichiers netlists résultant de la synthèse

séparée des modules sont alors prêts à être

insérés au niveau Top du design lors de la

synthèse de Top. En effet, lors

de la synthèse du Top, un module ne sera

resynthétisé que s'il a été modifié.

L'intérêt de la conception incrémentale est justement cette

validation modulaire qui apporte un gain de temps.

Sous ISE par exemple avec l'outil de synthèse XST, les

modules du design Top doivent être déclarés dans son

fichier vhdl du top comme des composants ayant l'attribut « Black box

». Cet attribut indique à l'outil de synthèse de ne pas

faire la synthèse du module lors de la synthèse du Top.

b) Le Placement et Routage (P&R)

Incrémental

Le principe est identique à celui de la synthèse

incrémentale. Ainsi, après modification d'un bloc un nouveau

P&R n'affecterait pas le P&R de la partie inchangée du

design.

3.1.3 Le Modular Design Flow pour la reconfiguration

partielle

a) Présentation [22]

Il s'agit d'une méthode de conception

incrémentale. A l'origine il permet à une équipe

d'ingénieurs de travailler indépendamment sur des modules d'un

design en vue d'une fusion postérieure et une implémentation sur

un FPGA unique. Comme décrit au paragraphe précédent, un

grand design est découpé en plusieurs modules en vue d'un travail

en équipe. Chaque concepteur de l`équipe implémente et

teste le(s) module(s) à sa charge séparément, et le chef

d'équipe définit la structure globale du design et intègre

les modules implémentés au niveau Top-Level du design

qui comprend (Figure 21) :

Figure 21 : Vue au niveau TOP d'un design modulaire

- Un ensemble de modules indépendants (mais synchrones et

pouvant communiquer par des interfaces appelés Bus macros).

- L'interface entre les modules (Bus macros).

- L'interface avec les pins (les E/S du design sont

déclarées au niveau Top).

Un fichier de contrainte (.ucf chez Xilinx) permet de

fixer les contraintes d'espace (pour les pins du FPGA à utiliser et la

position de chaque module sur le FPGA) et de temps (fréquence maximale

de fonctionnement). Chez Xilinx, ce fichier peut être soit écrit

soi-même, soit généré automatiquement par l'outil

Floorplaner, l'éditeur graphique de contraintes d'espace pour

les FPGAs Xilinx.

b) Modular Design Flow pour la reconfiguration

partielle

Le Modular Design flow par son approche modulaire est

particulièrement adapté à la conception d'applications

partiellement reconfigurables comme la nôtre ou un module entier

doit être reconfiguré. Mais le modular design flow pour la

reconfiguration partielle suggère pour des raisons pratiques que

toute conception doit avoir au niveau top deux parties homogènes

(à ne pas confondre avec les modules dont le nombre maximal est en

théorie égale au quart du nombre de colonnes de Slices) : une

partie fixe et une partie reconfigurable.

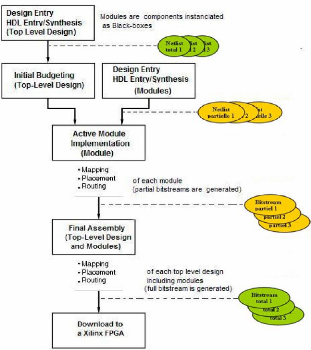

Figure 22 : Le flot Modular Design pour la reconfiguration

partielle Il se déroule en 4 étapes (Figure 22)

:

1. La Synthèse des modules et du design au niveau

top (Top-level Design).

2. L'Initial Budgeting qui détermine

approximativement la taille de chaque module à implémenter puis

lui attribue une zone sur le FPGA conformément aux contraintes de

placement et de temps.

3. L'Active Module Implémentation ; les

modules sont implémentés individuellement et dans des

répertoires séparés, et les bitstreams partiels sont

générés dans le cas de la reconfiguration partielle.

4. Le Final Assembly qui implémente le design

entier en assemblant tous les modules, puis génère son bitstream

complet qui permet de configurer le FPGA.

Nous décrirons en détail les étapes du

Modular Design dans un cas d'étude effectué plus loin.

3.2 Principe de l'Auto-Reconfiguration partielle et

dynamique

3.2.1 De la reconfiguration partielle

Sur la Figure 23 , le design Top1 est

constitué de 3 modules (Module 1, Module 2 et Module 3). Reconfigurer

partiellement ce design revient à le faire passer de Top1

à un nouveau design Top2 (resp. Top3) par remplacement du

Module 3 par le Module 3' (resp. Module 3'') conçu à

dessein pour occuper le même espace physique sur le FPGA et utiliser les

mêmes entrées/sorties. L'exemple de la figure 13 , ou le module

« Control » est remplacé par le module «

Video out » par reconfiguration partielle du FPGA l'illustre bien.

|

Figure 23 : Passage d'un Top à un autre par

reconfiguration partielle (remplacement du module 3).

|

|

Ainsi, soit un FPGA pouvant contenir i modules sur

des emplacements Ei de sa surface. Soit j le nombre de

designs pouvant occuper le même emplacement Ei. En supposant que

tous les modules soient reconfigurables (ce qui n'est pas possible dans le cas

de l'autoreconfiguration car le module chargé de reconfigurer

partiellement doit être fixe pour assurer l'intégrité du

circuit entre deux configurations), on peut facilement déduire qu'on a

i x j scénarii possibles de fonctionnement. Dans le cas de la

figure 23, les modules 1 et 2 sont fixes et le

module 3 reconfigurable : il ya donc 3 scenarii possibles

(Top1, Top2, Top3) pour 3 designs différents du module 3

(Module 3, Modules 3' et Module 3»).

3.2.2 De l'auto-reconfiguration dynamique

Nous entendons ici par Auto-reconfiguration le fait

que le processeur PPC405 integré au FPGA puisse partiellement

reconfigurer celui-ci. En effet, on peut également dire que le FPGA

s'auto-reconfigure partiellement. C'est effectivement le cas si on utilise un

FPGA avec un processeur soft core (Microblaze par exemple). Ayant

adopté une conception modulaire, il est également clair que le

module contenant le processeur et ses périphériques et

chargé de la reconfiguration partielle est fixe (non-reconfigurable).

La reconfiguration dynamique suppose que la

reconfiguration d'un bloc ou d'un module n'altère pas le fonctionnement

du reste de la puce. L'auto-reconfiguration est donc

intrinsèquement une reconfiguration dynamique.

3.3 Exemple de mise en oeuvre d'une application

auto-reconfigurable à l'aide

de ISE et EDK

3.3.0 Introduction

Nous allons détailler les étapes de la mise en

oeuvre de l'auto-reconfiguration à travers une étude de cas. La

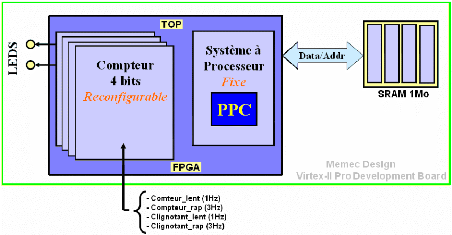

Figure 24 présente le schéma de principe de ce

système à deux modules, l'un fixe et l'autre reconfigurable. Les

bitstreams de reconfiguration du module reconfigurable peuvent être

chargés dans une mémoire de type SRAM ou Flash. Le FPGA

utilisé est le VirtexII Pro XVP7 que nous avons présenté

plus haut.

Une fois le FPGA configuré, une application

développée par nous (srp.c) permet au processeur PPC

intégré :

- De charger (via une connexion UART-HyperTerminal a un PC) des

bitstreams partiels

du module reconfigurable et de les stocker en mémoire SRAM

(externe à la puce).

- De reconfigurer dynamiquement et à la demande le module

reconfigurable.

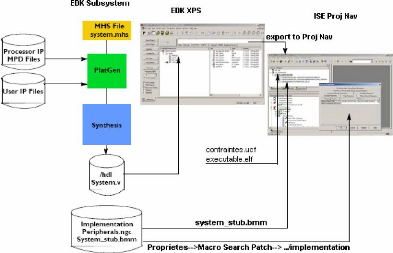

- L'environnement EDK (Embedded Development Kit) de

Xilinx a permis de bâtir

séparément le module fixe (système

à microprocesseur), de développer l'application pour le

processeur et de générer l'exécutable (environnement de

cross-compilation et de debuggage). Xilinx EDK est un ensemble d'outils

softwares pour la conception des systèmes à processeur

embarqué sur des circuits FPGAs Xilinx. A travers son environnement

graphique XPS (Xilinx Platform Studio), EDK facilite la création de

l'architecture matérielle du système a microprocesseur

(processeur et périphériques de communication, Figure

25) et fournit le

support logiciel (generation des pilotes, cross-compilation,

debuggage) permettant le developpement des applications pour le processeur

integre.

- L'environnement ISE (Integrated System Environment) a

permis d'integrer les deux

modules de la Figure 24 dans un design unique

(top.vhd) et de faire la synthèse. En effet, une fois que le

système à processeur est teste et valide sous EDK, il est

exporte vers ISE comme un sous-module reconfigurable afin de construire le

design global de la Figure 24. Après la synthèse du

design global sous ISE, le reste du flot de conception modulaire pour la

reconfiguration partielle (Figure 22) sera deroule par ecriture de

scripts appropries, ce flot n'etant pas automatise sous ISE.

Figure 24 : Etude de cas de l'auto-reconfiguration

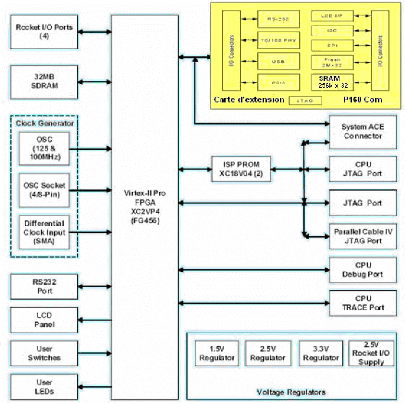

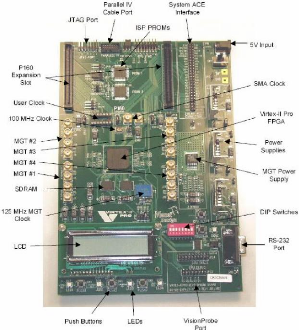

3.3.1 La plateforme matérielle de

développement, la carte Virtex-II Pro de Memec Design

Cette carte developpee par Memec Design comprend essentiellement

(Figure 25): - Un FPGA Virtex II Pro XVP7 ou XVP4

- Une SDRAM 32 Mo que nous n'avons pu utiliser comme memoire de

stockage des

configurations parce qu'elle n'est pas situee du côte du

FPGA où se trouve le module « Système à Processeur

».

- Deux horloges (100MHz et 125 MHz)

- Un ecran d'affichage LCD

- 4 LEDs

- 4 Boutons poussoirs

- 8 DIP switches

- Un port Série RS232 (physiquement connecté au

FPGA par ses pins du côté gauche,

et donc inutilisable par le module « Système à

Processeur » implémenté sur le côté droit de la

puce).

- Un port Jtag

Figure 25 : Vue schématique de la carte de

développement Virtex-II ProTM de Memec Design - Une

carte d'extension P160 Com (Figure 25, en gris).

Cette carte d'extension P160 Com comprend des ressources