II.6.2.2. Etape de traduction vers Colif :

Cette étape extrait les informations structurelles de

la description d'entrée (systemC), pour les mettre sous le format Colif

qui sera traité tout au long du flot. Les informations comportementales

et les informations «boîte noire » sont conservées.

Cette étape a été automatisée grâce aux

outils développés dans l'équipe par Wander

Cesário.

II.6.2.3. Etape d'allocation mémoire et de

synthèse de la communication :

Cette étape permet de passer d'une description du

niveau fonctionnel au niveau macroarchitecture.

L'allocation mémoire consiste en la définition

des blocs mémoires qui vont contenir les données de

l'application. Il s'agit généralement d'une heuristique

permettant de déterminer automatiquement une configuration optimale pour

réduire le coût en communication mémoire.

La synthèse de la communication consiste à

choisir les protocoles de communication et les éléments de calcul

(processeurs, ASIC, etc.) qui seront utilisés. Dans l'état actuel

du flot, aucun outil ne permet d'effectuer cette synthèse de

communication. Cette opération est donc effectuée à la

main.

Des résultats de simulation au niveau macroarchitecture

(voir le paragraphe II.6.2.9) permettent de guider les choix pour les

protocoles. A l'avenir, il est prévu d'intégrer une

méthodologie et des outils permettant d'automatiser les choix à

l'aide d'une bibliothèque de résultats de simulation.

II.6.2.4. Etape d'affectation et d'optimisation de

mémoire :

Une fois que les blocs mémoire ont été

décidés, il est possible de leur assigner les données.

Cette opération est effectuée au cours de cette étape en

parallèle avec l'optimisation des accès mémoire.

II.6.2.5. Etape de génération

d'architecture mémoire :

Durant cette étape, les types de mémoires, leurs

contrôleurs et leurs interfaces sont générés

à partir d'une bibliothèque. Le principe de cette

génération est celui d'un assemblage de blocs de la

bibliothèque. Cet assemblage est guidé par les choix d'allocation

et de synthèse (voir le paragraphe II.6.2.3).

II.6.2.6 Etape de génération d'interfaces

matérielles :

La génération d'interfaces matérielles

permet d'interconnecter les divers éléments de calcul : en effet

ces éléments ne sont pas tous compatibles entre eux. Ces

interfaces permettent aussi de réaliser de protocoles de communication

non supportés nativement par les éléments.

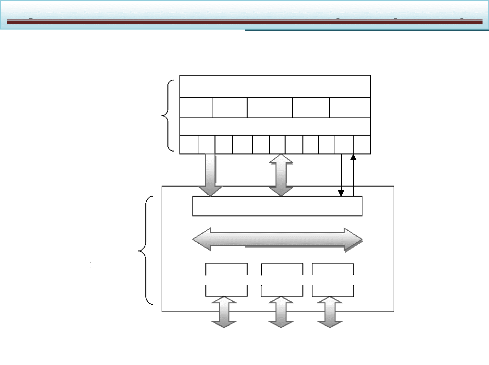

Cette étape, est basée sur un assemblage de

blocs à partir d'une bibliothèque. Le modèle d'interface

généré au sein du flot est présenté figure

II.11. L'interface est constituée de trois parties. Une première

partie, dépendante de l'élément de calcul (processeur),

fait le pont entre son bus et celui de l'interface. La deuxième partie

est le bus de l'interface, et la dernière est l'ensemble des

contrôleurs de communication qui réalisent les protocoles. Ce

découpage permet de générer aisément des interfaces

pour tout type de processeur et tout type de protocole sans que la

bibliothèque soit trop grande.

Figure II.11 : Génération d'interfaces

matérielles et logicielles

Interface

matérielle

Processeur

Application

API

Noyau

ES

PILOT

Bus interne

Bus adresse bus données contrôle

Coprocesseurs de communication

Pont vers le bus interne

|