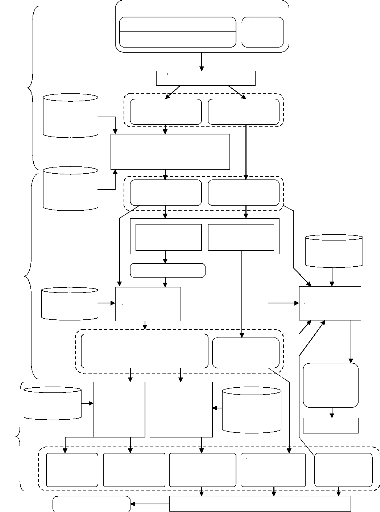

II.6.2. Architecture détaillée du flot :

Ce flot global est présenté sur la figure II.10.

Il part d'une spécification architecturale et comportementale du

système à concevoir. La description est alors raffinée de

niveaux d'abstraction en niveaux d'abstraction. En sortie, nous obtenons le

code logiciel et matériel réalisant l'application.

II.6.2.1. L'entrée du flot au niveau fonctionnel

:

En entrée du flot, nous prenons une description dans le

langage systemC. Ce langage permet de décrire la structure et le

comportement d'un système logiciel et matériel. Il est

basé sur le langage C++ étendu avec des bibliothèques

permettant la modélisation et la simulation de systèmes

logiciels/matériels globalement synchrones, ou asynchrones avec un

modèle à événements proches de celui du VHDL.

Cette description peut être effectuée au niveau

fonctionnel ou aux niveaux inférieurs. Il est aussi possible de combiner

les niveaux. Elle donne les informations sur la structure, et

éventuellement le comportement. Si certains composants sont fournis sans

comportement, ils sont considérés comme des boîtes

noires.

Cependant il était préférable que nous

possédions l'entière maîtrise du flot et donc qu'il ne

dépende pas d'un langage d'entrée externe à notre groupe.

C'est pourquoi la première étape du flot consiste à

convertir la description system C en une description Colif.

REMARQUE :

Lorsqu'un module représente un processeur, nous

considérons qu'il est accompagné par une mémoire locale

dans laquelle sont stockés le code et les données locales du

logiciel que le processeur doit exécuter. Tout au long de ce travail,

dès que nous parlerons de processeur, nous supposerons implicitement

l'existence de cette mémoire locale. Dans le cas où le processeur

est un microcontrôleur, les périphériques

intégrés seront eux aussi encapsulés dans l'enveloppe

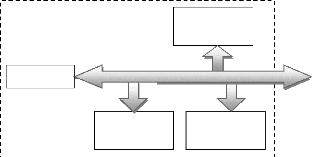

représentant le processeur. La figure II.9 montre l'architecture

représentée par un module processeur.

Processeur

Périphérique

local

Bus du processeur

Mémoire

local

Périphérique

local

Figure II.9. Un module processeur

Niveau micro-architecture

Niveau fonctionnel

Niveau macroarchitecture

Bibliothèque

d'interfaces

Bibliothèque

de mémoire

Code des interfaces matérielles

Bibliothèque

de

modèles

mémoire

Bibliothèque

de

commun-

ication

Système monopuce

Architecture Colif annotée

macro-

architecture avec mémoire

Génération

d'interfaces

matérielles

Architecture Colif micro-architecture

Allocation mémoire globales

SystemC annoté

Génération

d'architecture

mémoire

Description du comportement

Description de l'architecture

Architecture Colif

fonctionnelle

Architecture Colif

macroarchitecture

Table d'allocations

Affectations

mémoire

Génération

de

systèmes

d'exploitation

(interfaces

logicielles)

Traduction vers Colif

Code systèmes

d'exploitation

raffinement : synthèse de

communication

Optimisations

d'accès

mémoire

Comportement

(ex. C++)

Comportement

(ex. C++)

Comportement

optimisé

Compilation / Synthèse

Bibliothèque

de

système

d'exploitation

Comportement optimisé

Boites

noires

Génération

d'architecture

mémoire

Description

multilangage

multiniveau

simulable

Cosimulation

Bibliothèque

de simulation

Composants

existants

Figure II.10 : Le flot de conception

générale pour les systèmes monopuces

Chapitre II conception des logiciels embarqués

|