II.3. La conception des systèmes sur puces :

Le flot de conception est généralement

découpé en deux parties, la partie frontale et la partie dorsale

du flot (en anglais ces parties sont appelées front-end et

back-end). La première partie consiste à raffiner les

spécifications initiales pour produire une réalisation de haut

niveau. La partie dorsale du flot réalise les étapes de

conception de bas niveau pour aller à la puce. Le point de

Chapitre II conception des logiciels embarqués

rencontre constitue un contrat (en anglais sign-off)

permettant de sous-traiter la partie dorsale du flot. Au cours des

années, la réalisation de haut niveau faisant l'objet du contrat

à évolué du simple dessin des masques aux modèles

de portes et est en passe d'atteindre le niveau transfert de registre. Il est

prévu que cette évolution continue pour atteindre le niveau

micro-architecture puis le niveau architecture de système contenant

à la fois les parties matérielles (composants et interconnexions)

et les parties logicielles (programmes d'applications et systèmes

d'exploitation).

La partie frontale du flot part d'une spécification

système qui permet de fixer les principales contraintes du produit

à réaliser. Ce modèle sera aussi utilisé pour

l'exploration d'architecture afin de fixer la solution architecturale qui sera

réalisée. Suit alors la conception de cette solution. Cette

étape comporte trois types d'actions ; la conception des composants

logiciels, la conception des composants matériels et la conception des

interfaces logicielles/matérielles.

Le résultat de cette partie est actuellement une

micro-architecture de l'ensemble du système. Les parties

matérielles sont détaillées au niveau transfert de

registre (description au niveau du cycle d'horloge). Dans le cas où le

système contient des parties logicielles exécutées sur un

ou plusieurs processeurs embarqués, elles sont décrites au niveau

de l'instruction (assembleur)

La partie dorsale comprend la conception des parties

matérielles en passant par la conception logique et la conception

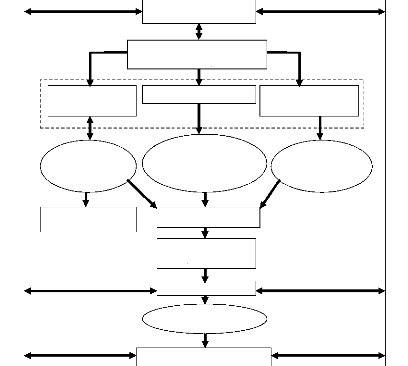

physique. La figure II.3 montre une vue simplifiée de ce flot. Les

rectangles désignent des modèles de description et les ovales des

outils.

Verification, validation (tome!)

Architecture

Code assembleur

Raffinement du Raffinement de la

Synthèse

Logiciel (tome3) communication (tome3)

comportementale

(tome1)

Spécification des parties logicielles

Exploration d'architecture

(tome1)

Produit (niveau physique)

Spécification système

Conception physique

(tome2)

Interconnexion

Conception logique

(tome2)

Micro-architecture

Ports logiques

Spécification des

parties

matérielles

Test (Tome2)

Figure II.3 : le flot de conception

système

Ce flot considère cinq niveaux d'abstraction : le

niveau système, le niveau architecture et le niveau microarchitecture,

le niveau porte et le niveau physique. Au niveau système le circuit est

spécifié au niveau des transactions entre les

éléments de calcul : un ensemble de modules hiérarchiques

et de processus communiquant par protocoles de communication de haut niveau par

l'intermédiaire de canaux abstraits. Un canal peut cacher des protocoles

de communication de haut niveau et des primitives de communication qui

manipulent des types de données abstrait. A ce niveau, les modules

peuvent être décrits en utilisant différents langages et/ou

en utilisant différents niveaux d'abstraction. La cosimulation est

utilisée pour valider la fonctionnalité du système. Ce

modèle peut être utilisé pour explorer l'espace des

solutions architecturales et fixer les grandes lignes de l'architecture. Cette

étape est généralement réalisée à

l'aide d'outils de simulation et d'estimation de performances.

Le deuxième niveau d'abstraction représente une

architecture abstraite qu'on appelle macroarchitecture, ce modèle est

composé d'un ensemble de modules reliés ensemble par des fils

logiques. Chaque module représente un processeur dans l'architecture

finale. Ceci peut être un processeur logiciel (par exemple : un DSP ou un

microcontrôleur exécutant le logiciel), un processeur

matériel (un composant spécifique) ou un module existant

(mémoire globale, périphérique, contrôleur de bus,

etc.). Les fils logiques sont des canaux abstraits qui transfèrent des

types de données fixes (par exemple : nombre entier ou flottant) et

peuvent cacher des protocoles de bas niveau (par exemple : poignée de

main, transfert en mode rafale). Les différents modules peuvent

être décrits en utilisant un ou plusieurs langages. La

cosimulation peut être utilisée pour valider ce découpage

architectural. Cette macroarchitecture peut être utilisée par

différentes équipes pour réaliser les composants

matériels, les composants logiciels et l'intégration des

différents composants. Le résultat de ce flot est une

macroarchitecture du système décrite au niveau transfert de

registre. Ce modèle contient tout les détails de la communication

entre les composants. Les couches de communication logicielles peuvent

comporter un système d'exploitation spécifique (OS). Les couches

de communication matérielles comportent les bus et autres dispositifs

permettent de router les informations entre les composants. Les blocs

matériels sont raffinés au niveau du cycle d'horloge. Finalement,

les blocs existants (souvent appelés IP de l'anglais Intellectual

Property) sont enveloppés dans des interfaces afin de les adapter

aux bus et réseaux de communication utilisés. La connexion entre

les différents blocs matériels est faite par les fils physiques

qui mettent en application les protocoles choisis. Les composants logiciels

communiquent entre eux et avec l'extérieur via des appels système

à l'OS.

Le niveau porte détaille le système au niveau

des délais élémentaires des transferts entre les portes de

base. Finalement, le niveau physique représente les dessins des

masques.

|