|

Ecole Polytechnique De Tunisie

Option : Signaux et Systèmes

Rapport de Projet de Fin d'Etudes

Effectué du 11 février au 11 juin 2008

Etude et implémentation d'un système sans fil

multi-antennes dans un contexte MC-CDMA

Organisme d'accueil : TELNE

Elaboré par : Mohamed MAALEJ

Encadré par : Mme. Ines KAMMOUN-JEMAL M. Ameur SBOUI

13.édicace

~edédie ce tra~ail, A men cher père

`eur les sacri~ices que mus ne cessez de consentir, peur ms

encouragements t~utes les heures de mes études, peur mis conseils

teujours prediguées arec am~ur, peur la cen~iance que ;eus amez

crée en mei

A la mémeire de ma très chère

mère,

A la mémeire de lafemme queje deis teut,j~aurais tant

aimé ;eus mir à mes cotés cesjeur. C~us neus aurez

quitté t"t, mais mitre tendresse et p~tre patience resterent

gravées dans men coeur et men esprit peur teujours.

A ma chère bele mère,

`eur les sacri~ices déployés à men

égard, peur mes encouragements et p~tre ameur sans limites.

A mes~rères et mes chères soeurs, ;etre

gentilesse et mitre sympathie sent exemplaires, ;eus dtes peur

mei l~eremple de benté et de l~henndteté.

A teus mes amis, peur mitre amour et mes encouragements, je peus

seuhaite beauceup de benheur et de succès.

AVANT PROPOS

TELNET est une société d'ingénierie et de

conseil dans l'innovation et les hautes technologies oeuvrant dans les secteurs

des télécoms et multimédia, auto motive et transport,

avionique et défense, sécurité et carte à puce,

électronique et industrie, systèmes d'information et

ingénierie mécanique.

TELNET a été créée en 1994 pour

répondre à une demande croissante en développements

logiciels, en 2006, Telnet a obtenu le niveau 5 selon le modèle CMMI.

Depuis novembre 2007, TELNET opère à partir de

quatre sites différents, trois sites en Tunisie et un en France.

Le domaine des activités des quatre sites concerne

principalement

Les études logicielles

Conception et développement de produits logiciels dans

divers domaines d'activités Télécoms, Multimédia,

Transport, Consumer Product, Sécurité et Défense,etc..

Les systèmes électroniques

Conception et design en électronique et en

microélectronique, Test et validation de systèmes

électroniques.

Les Réseaux et Télécoms

La réalisation de prestations d'ingénierie dans les

domaines des réseaux de télécommunication

L'ingénierie Produit Mécanique CAO & Simulation

Mécanique FAO et Process d'industrialisation

Le site de Sfax se distingue des autres sites par un

département de recherche et développement

spécialisé en micro-électronique et en communications

radio-mobiles. Dans ce sens, une équipe a été

formée pour développer des compétences et métiers

spécialisés dans les nouvelles techniques de communication

numérique, de description matérielles et implémentation

électronique.

REMERCIEMENTS

Je remercie M. Hassib Ellouze chef d'opération à

TELNET de m'avoir accepté au sein du site de Sfax.

Je tiens à exprimer ma profonde reconnaissance à

Mme. Inès Kammoun-Jemal, Maître assistante à l'Institut

Supérieur d'Electronique et de Communication de Sfax (ISECS), qui a

proposé et a encadré mon projet de fin d'études, pour son

aide précieuse, ses conseils fructueux et son suivi de ce travail avec

une extrême bienveillance. Je tiens à remercier également

M. Ameur Sboui, Ingénieur chercheur à Telnet pour son

co-encadrement et son aide précieuse dans la partie

implémentation.

Je remercie également M. Mourad Loulou Maître de

conférences à l'Ecole National des Ingénieurs de Sfax

(ENIS) pour ses conseils et l'intérêt qu'il a su manifester pour

mon travail.

Je remercie Mme. Sarra Ben Lagha, Professeur à l'Ecole

Polytechnique de Tunisie, qui a bien voulu être la responsable de mon

stage du coté de l'EPT.

Mes remerciements s'adressent également à tous les

enseignants de l'EPT et à tous les membres de jury pour avoir

accepté de juger ce modeste travail.

REsuME

Les travaux effectués dans ce mémoire font

l'objet d'une contribution à la conception de circuits

intégrés complexes pour les applications radio-mobile, en

particulier pour les systèmes multiantennes. Les systèmes

à antennes multiples permettent d'offrir des débits

élevés sur des canaux à évanouissements, mais une

source importante de dégradation des performances dans ces

systèmes est la sélectivité fréquentielle du canal.

Une solution pour combattre la sélectivité fréquentielle

du canal consiste à utiliser la modulation OFDM.

L'objectif de ce projet de fin d'études est

d'étudier et de proposer une description matérielle en VHDL d'un

système multi-antennes dans un contexte MC-CDMA. La technique MC-CDMA

correspond à la combinaison entre la technique d'accès CDMA et la

modulation OFDM où l'étalement des données est

réalisé dans le domaine fréquentiel.

Dans ce projet, on commence par évaluer les

performances du système MIMO-MC-CDMA à travers une

implémentation sur Matlab. Ensuite, on propose une architecture

matérielle du système par une description en VHDL des

différents composants de l'émetteur et du récepteur. Par

ailleurs, on implémente cette chaîne sur une architecture

matérielle reconfigurable à base de circuits FPGAs, on fournit

les résultats de synthèse au niveau RTL et on analyse les

performances de l'architecture proposée en termes de complexité

et de rapidité.

Mots clés : Les systèmes multi-antennes, OFDM,

MC-CDMA, VHDL, FPGA.

ABSTRACT

The works presented in this report constitutes a contribution to

the design of complex integrated circuits for wireless applications, in

particular for the multi-antenna systems.

Multi-antenna systems promise very high data rate on

scattering-rich wireless channels, but an important source of performances

degradation in these systems is the frequency selectivity of the channel. To

combat the frequency selectivity of the channel, a solution achieving a good

complexity/performance trade-off is to use OFDM modulation.

The aim of this project is to study and to propose a material

description using VHDL of a multiantenna system in a MC-CDMA context. The

MC-CDMA technique corresponds to the combination between the CDMA technique and

the OFDM modulation where the data spreading takes place in the frequency

domain.

In this project, we begin by evaluating the performances of

MIMO-MC-CDMA system through an implementation on Matlab. Then, we propose a

material architecture of the system by a VHDL description of different

components for both the transmitter and the receiver. Morover, we implement

this chain on a reconfigurable material architecture based on FPGA circuits, we

provide the synthesis result at RTL level and we analyze the proposed

architecture performance in terms of complexity and timing features.

Key-words: Multi-antenna system, OFDM, MC-CDMA, VHDL, FPGA.

TABLE DES MATIERES

INTRODUCTION GÉNÉRALE 1

Chapitre1 3

La Technique MC-CDMA 3

1. Introduction 3

2. Les composantes de base d'une chaîne de transmission

numérique 3

2.1. Le codeur et le décodeur de canal 4

2.2. La modulation/démodulation numérique 5

2.2.1. Modulation à déplacement d'amplitude ASK

(Amplitude Shift Keying) 6

2.2.2. Modulation à déplacement de phase PSK

(Phase Shift Keying) 6

2.2.3. Modulation d'amplitude en quadrature QAM (Quadrature

Amplitude Modulation) 6

3. Le canal radio-mobile 7

3.1. Effet multi-trajet d'un canal radio 7

3.2. Etalement temporel 9

3.3. Etalement fréquentiel : effet Doppler 9

3.4. Modélisation du canal à

évanouissements lents 10

4. La modulation OFDM 11

4.1. Principe de l'OFDM 11

4.2. Modulation par la Transformée de Fourier

Discrète DFT 12

4.3. Introduction de l'intervalle de garde en OFDM 12

5. Les techniques d'accès multiple 13

5.1. Accès multiple à répartition par

temps 14

5.2. Accès multiple à répartition par

fréquence 14

5.3. Accès multiple à répartition par code

14

6. La technique CDMA 14

6.1. Principe du CDMA 15

6.2. Modélisation du système CDMA 17

7. La technique CDMA associée à la modulation

multi-porteuses 17

7.1. Partie émettrice 18

7.2. Partie réceptrice 19

7.3. Les techniques de détection en MC-CDMA 20

7.3.1. Détection mono-utilisateur 21

7.3.2. Détection multi-utilisateurs 21

8. Conclusion 22

Chapitre 2 23

Multiplexage spatial dans un contexte CDMA 23

1. Introduction 23

2. Techniques de diversité 24

2.1. Diversité temporelle 24

2.2. Diversité fréquentielle 25

2.3. Diversité spatiale 25

3. Les systèmes MIMO 26

3.1. Le codage espace-temps 27

3.1.1. Les codes ST en treillis 28

3.1.2. Les codes ST en bloc 28

3.2. Multiplexage spatial 29

3.3. Les techniques de détection pour le multiplexage

spatial 29

3.3.1. Techniques de détection linéaires 30

3.3.2. Technique de détection non linéaire

à annulation successive d'interférences 31

3.4. Résultats de simulation 32

4. Association entre multiplexage spatial et la technique

MC-CDMA 35

4.1. Conception de la chaîne MIMO associée au

MC-CDMA 35

4.2. Modélisation de la chaîne de transmission

MIMO-MC-CDMA 36

4.3. Techniques d'égalisation pour la chaîne

MIMO-MC-CDMA 38

4.4. Evaluation des performances du système MIMO-MC-CDMA

39

4.4.1. Cas de la chaîne sans codage de canal 40

4.4.2. Cas de la chaîne avec codage convolutif 42

5. Conclusion 44

Chapitre 3 46

Implémentation matérielle et analyse de

performances 46

1. Introduction 46

2. Le circuit FPGA Stratix II.GX 46

3. Flot de conception adopté et environnement de

synthèse 48

4. Spécification fonctionnelle et résultats

d'implémentation 49

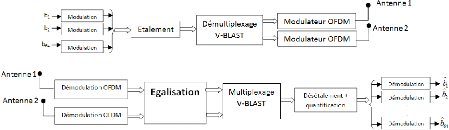

4.1. Architecture de la chaîne MIMO associée au

MC-CDMA 49

4.2. Architecture des blocs utilisés dans la chaîne

50

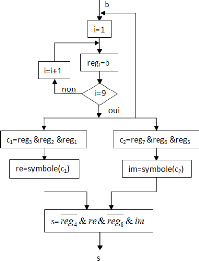

4.2.1. Bloc de modulation 256-QAM 50

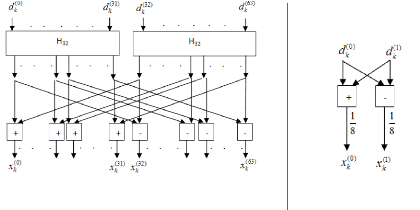

4.2.2. Bloc étalement 51

4.2.3. Bloc de démultiplexage spatial V-BLAST pour 2

antennes 54

4.2.4. Bloc modulateur OFDM 55

4.2.5. Bloc démodulateur OFDM 60

4.2.6. Bloc de l'égalisation 62

4.2.7. Bloc de multiplexage spatial de 2 antennes 68

4.2.8. Bloc "désétalement + quantification" 68

4.2.9. Bloc démodulation 70

5. Optimisation et analyse de performances de la chaîne

71

6. Conclusion 75

CONCLUSION ET PERSPECTIVES 76

RÉFÉRENCES BIBLIOGRAPHIQUES 78

ANNEXE 80

DES

LISTE FIGURES

FIGURE 1.1. COMPOSANTES DE BASE D'UNE CHAINE DE TRANSMISSION

4

FIGURE 1.2. CODEUR CONVOLUTIF (K=1,N=3 ET (M+1)=3) 4

FIGURE 1.3. CONSTELLATION DE LA MODULATION M-ASK 6

FIGURE 1.4. CONSTELLATION DE LA MODULATION 8-ASK 6

FIGURE 1.5. CONSTELLATION DES MODULATIONS BPSK, QPSK ET 8-PSK

7

FIGURE 1.6. CONSTELLATION DE 16-QAM UTILISANT LE CODAGE DE GREY

7

FIGURE 1.7. MODELISATION DU PHENOMENE DE TRAJETS MULTIPLES 8

FIGURE 1.8. INTRODUCTION DE L'INTERVALLE DE GARDE AU SYMBOLE OFDM

TRANSMIS 13

FIGURE 1.9. CHAINE D'EMISSION ET DE RECEPTION DU MODULATEUR OFDM

13

FIGURE 1.10. LA TECHNIQUE TDMA 14

FIGURE 1.11. LA TECHNIQUE FDMA 14

FIGURE 1.12. LA TECHNIQUE CDMA 14

FIGURE 1.13. ETALEMENT PAR SEQUENCES DIRECTES 15

FIGURE 1.14. CIRCUIT D'EMISSION POUR UN UTILISATEUR DE LA

TECHNIQUE MC-CDMA 18

FIGURE 1.15. CIRCUIT DE RECEPTION POUR UN UTILISATEUR DE LA

TECHNIQUE MC-CDMA 20

FIGURE 2.1. EMISSION DU MEME SIGNAL A DES INSTANTS SEPARES PAR LE

TEMPS DE COHERENCE DU CANAL 24

FIGURE 2.2. EMISSION DU MEME SIGNAL SUR DES FREQUENCES

DIFFERENTES 24

FIGURE 2.3. DIVERSITE SPATIALE A L'EMISSION 25

FIGURE 2.4. DIVERSITE SPATIALE A LA RECEPTION 25

FIGURE 2.5. REPRESENTATION DES DIFFERENTS TRAJETS ENTRE ANTENNES

EMETTRICES ET RECEPTRICES 26

FIGURE 2.6. SCHEMA D'ALAMOUTI POUR LE CAS DES ANTENNES EN

EMISSION 28

FIGURE 2.7. DIAGRAMME DE LA TECHNIQUE DE DEMULTIPLEXAGE V-BLAST

28

FIGURE 2.8. BLOC D'EGALISATION POUR LE MULTIPLEXAGE SPATIAL 29

FIGURE 2.9. TEB EN FONCTION DU RSB SUR UN CANAL DE RAYLEIGH.

33

FIGURE 2.10. TEB EN FONCTION DU RSB EN UTILISANT LES RECEPTEURS

ZF ET MMSE 34

FIGURE 2.11. TEB EN FONCTION DU RSB EN UTILISANT UN ALGORITHME

SIC 34

FIGURE 2.12. CHAINE D'EMISSION DE LA TECHNIQUE MIMO-MC-CDMA 36

FIGURE 2.13. CHAINE DE RECEPTION DE LA TECHNIQUE MIMO-MC-CDMA

36

FIGURE 2.14. TEB EN FONCTION DU RSB POUR LES EGALISEURS A CRITERE

ZF ET MMSE 40

FIGURE 2.15. TEB EN FONCTION DU RSB POUR DES TRANSMISSIONS A

PLEIN CHARGE 41

FIGURE 2.16. TEB EN FONCTION DU RSB POUR LES DETECTIONS

MONO-UTILISATEUR ET MULTI-UTILISATEURS 41

FIGURE 2.17. TEB EN FONCTION DU RSB POUR L'ALGORITHME SIC 42

FIGURE 2.18. EMETTEUR M IMO-MC-CDMA AVEC CODAGE DE CANAL SUIVI

D'UN ENTRELACEUR 43

FIGURE 2.19. RECEPTEUR M IM O-MC-CDMA AVEC DESENTRELACEUR SUIVI

D'UN DECODAGE DE CANAL 43

FIGURE 2.20. TEB EN FONCTION DU RSB POUR LE SYSTEME MIMO-MC-CDMA

UTILISANT UN CODAGE DE CANAL 44

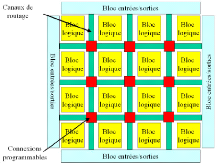

FIGURE 3.1. BLOC DIAGRAMME D'UN FPGA 47

FIGURE 3.2. FLOT DE CONCEPTION DE L'OUTIL QUARTUS 48

FIGURE 3.3. CIRCUITS D'EMISSION ET DE RECEPTION IMPLEMENTES 49

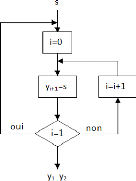

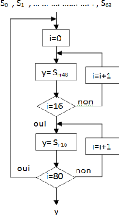

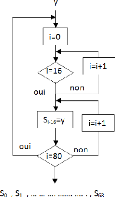

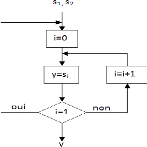

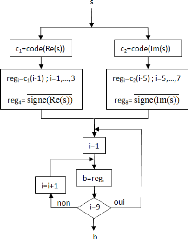

FIGURE 3.4. ORGANIGRAMME DU MODULATEUR 256-QAM 51

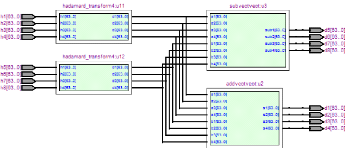

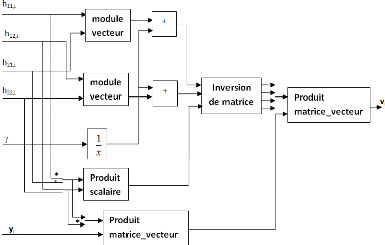

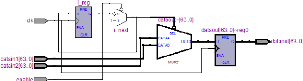

FIGURE 3.5. ARCHITECTURE DU BLOC ETALEMENT 53

FIGURE 3.6. FHT D'ORDRE 2 53

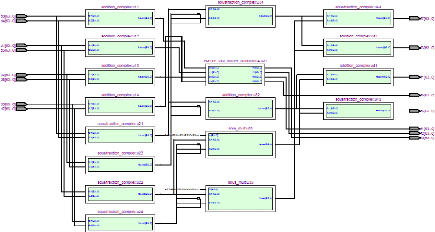

FIGURE 3.7. SCHEMA RTL DU FHT A L'ORDRE 8 53

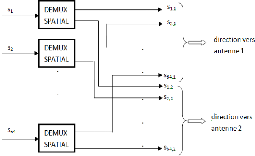

FIGURE 3.8. BLOC DE DEMULTIPLEXAGE V-BLAST 54

FIGURE 3.9. ORGANIGRAMME D'UN "DEMUX SPATIAL" 54

FIGURE 3.10. SCHEMA RTL DU BLOC "DEMUX SPATIAL" 54

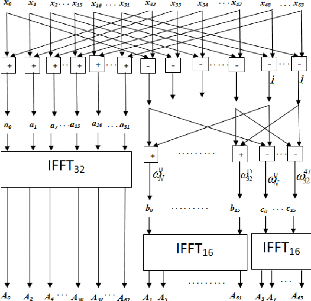

FIGURE 3.11. ARCHITECTURE DU MODULATEUR OFDM 55

FIGURE 3.12. ARCHITECTURE DU BLOC IFFT 58

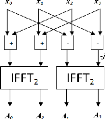

FIGURE 3.13. BLOC D'UNE IFFT A L'ORDRE 2 58

FIGURE 3.14. BLOC D'UNE IFFT A L'ORDRE 4 58

FIGURE 3.15. SCHEMA RTL D'UNE IFFT A L'ORDRE 8 59

FIGURE 3.16. ORGANIGRAMME DU BLOC DE CONVERSION P/S + 60

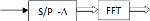

FIGURE 3.17. DIAGRAMME EN BLOC DU DEMODULATEUR OFDM 60

FIGURE 3.18. ORGANIGRAMME DU BLOC DE CONVERSION S/P - 61

FIGURE 3.19. ARCHITECTURE D'UNE FFT A L'ORDRE 2. 62

FIGURE 3.20. ARCHITECTURE DE L'EGALISEUR MULTI-UTILISATEURS A

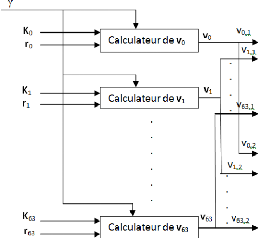

CRITERE MMSE. 65

FIGURE 3.21. ARCHITECTURE DU CALCULATEUR DE VI EN

FONCTION DE HRT,I , YI ET 66

FIGURE 3.22. SCHEMA RTL DU SOUS-BLOC "MODULE VECTEUR" 66

FIGURE 3.23 SCHEMA RTL DU SOUS-BLOC "PRODUIT MATRICE_VECTEUR"

66

FIGURE 3.24. SCHEMA RTL DU SOUS-BLOC INVERSION DE MATRICE 66

FIGURE 3.25. SCHEMA RTL DU SOUS-BLOC PRODUIT SCALAIRE 67

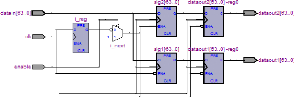

FIGURE 3.26. DIAGRAMME DU BLOC DE MULTIPLEXEUR SPATIAL 68

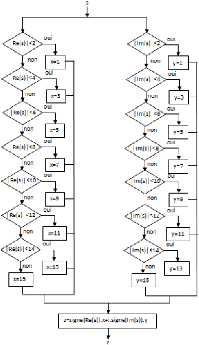

FIGURE 3.27. ORGANIGRAMME D'UN MULTIPLEXEUR 68

FIGURE 3.28. SCHEMA RTL D'UN MULTIPLEXEUR SPATIAL 68

FIGURE 3.29. SCHEMA BLOC DE "DESETALEMENT + QUANTIFICATION"

69

FIGURE 3.30. ORGANIGRAMME DU QUANTIFICATEUR 256-QAM 70

FIGURE 3.31. ORGANIGRAMME DU BLOC DE DEMODULATION 71

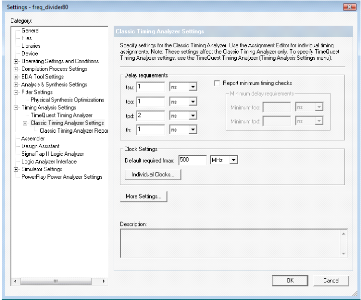

FIGURE 3.32. CONFIGURATION DES PARAMETRES DE TIMING 73

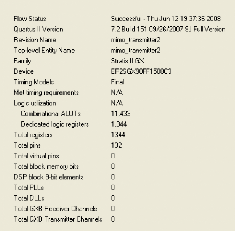

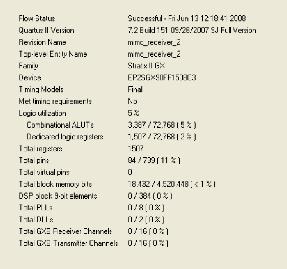

FIGURE 3.32. RESULTAT DE SYNTHESE DE LA CHAINE D'EMISSION DU

SYSTEME MI MO-MC-CDMA 74

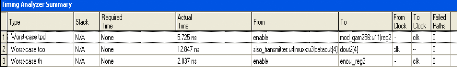

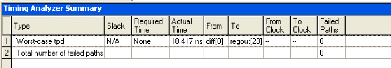

FIGURE 3.33. ANALYSE DE TIMING DE LA CHAINE D'EMISSION DU SYSTEME

MI MO-MC-CDMA 74

FIGURE 3.34. RESULTAT DE SYNTHESE DE LA CHAINE DE RECEPTION DU

SYSTEME M IMO-MC-CDMA 74

FIGURE 3.35. ANALYSE DE TIMING DE LA CHAINE DE RECEPTION DU

SYSTEME MIMO-MC-CDMA 75

LISTE DES TABLEAUX

ABLEAU 3.1. TABLE D'ASSIGNATION DES SYMBOLES EN FONCTION DU CODE

51

ABLEAU 3.2. TABLE DES PARAMETRES ENTREES/SORTIES DU BLOC DE

MODULATION 52

ABLEAU 3.3. RESULTAT DE SYNTHESE DU BLOC MODULATION 52

ABLEAU 3.4. TABLE DES PARAMETRES ENTREES/SORTIES DU BLOC DE

ETALEMENT 53

ABLEAU 3.5. RESULTAT DE SYNTHESE DU BLOC FHT 8 54

ABLEAU 3.6. TABLE DES PARAMETRES ENTREES/SORTIES DU BLOC DE

DEMULTIPLEXAGE V-BLAST 55

ABLEAU 3.7. RESULTAT DE SYNTHESE DU BLOC DE DEMULTIPLEXAGE

V-BLAST 55

ABLEAU 3.8. TABLE DES PARAMETRES ENTREES/SORTIES DU BLOC IFFT

58

ABLEAU 3.9. RESULTAT DE SYNTHESE DU BLOC IFFT 59

ABLEAU 3.10. RESULTAT DE SYNTHESE DU BLOC P/S + 59

ABLEAU 3.11. RESULTAT DE SYNTHESE DU BLOC S/P - 61

ABLEAU 3.12. TABLE DES PARAMETRES ENTREES/SORTIES DU BLOC FFT

62

ABLEAU 3.13. RESULTAT DE SYNTHESE DU BLOC IFFT 62

ABLEAU 3.14. RESULTAT DE SYNTHESE DU BLOC CALCULATEUR UTILISE

POUR LE BLOC EGALISEUR 67

ABLEAU 3.15. TABLE DES PARAMETRES ENTREES/SORTIES DU BLOC

EGALISEUR MULTI-UTILISATEURS 67

ABLEAU 3.16. TABLE DES PARAMETRES ENTREES/SORTIES DU BLOC

MULTIPLEXEUR SPATIAL 69

ABLEAU 3.17. RESULTAT DE SYNTHESE DU BLOC-BLOC CALCULATEUR

UTILISE POUR LE BLOC MULTIPLEXEUR SPATIAL 69

ABLEAU 3.19. RESULTAT DE

SYNTHESE DU BLOC-BLOC CALCULATEUR UTILISE POUR LE BLOC QUANTIFICATEUR

70

ABLEAU 3.20. TABLE DES PARAMETRES ENTREES/SORTIES DU BLOC

DEMODULATION 71

ABLEAU 3.21. RESULTAT DE SYNTHESE DU BLOC-BLOC CALCULATEUR

UTILISE POUR LE BLOC DEMODULATION 71

LISTE DES ABREVIATIONS

Dans ce rapport, plusieurs abréviations sont

utilisées. On les rappelle maintenant et on donne leurs

significations :

ALM Adaptive Logic Module

ASK Amplitude Shift Keying

BBAG Bruit Blanc Additif Gaussien

BLAST Bell Labs Layered Space-Time

BPSK Binary Phase Shift Keying

CDMA Code Division Multiple Access

D-BLAST Diagonal Bell Labs Layered Space-Time

DFT Discret Fourier Transform

DS-CDMA Direct Sequence Code Division Multiple Access

DSP Digital Signal Processing

FDMA Frequency Division Multiple Access

FFT Fast Fourier Transform

FH-CDMA Frequency Hopping Code Division Multiple Access

FHT Fast Hadamard Transform

FPGA Field Programmable Gate Array

IDFT Inverse Discret Fourier Transform

IFFT Inverse Fast Fourier Transform

IFHT Inverse Fast Hadamard Transform

IP Intellectual Property

LUT Look-U p Table

MC-CDMA Multi-Carrier Code Division Multiple Access

MIMO Multiple Input Multiple Output

MMSE Minimal Mean Square Error

MUD Multi-User Detection

OFDM Orthogonal Frequency Division Multiplex

PIC Parallel Interference Cancellation

PLL Phase Looked Loop

PSK Phase Shift Keying

QAM Quadrature Amplitude Modulation

QPSK Quadrature Phase Shift Keying

RAM Random Access Memory

RIF Réponse Impulsionnelle Finie

RII Réponse Impulsionnelle Infinie

RSB Rapport Signal à Bruit

RTL Register Transfer Level

SIC Successive Interference Cancellation

SNR Signal to Noise Ratio

ST Space-Time

SUD Single User Detection

TDMA Time Division Multiple Access

TEB Taux d'Erreur Binaire

V-BLAST Vertical Bell Labs Layered Space-Time

VHDL Very high speed integrated circuit Hardware Description

Language

ZF Zero Forcing

LISTE DES NOTATIONS

On regroupe ci-dessous les principales notations utilisées

dans les différents chapitres du rapport.

(.)T Transposition

(.)† ou (.)* Transconjugaison

(.)-1 Inversion

|

Norme euclidienne du vecteur x

|

Trace(X) Trace de la matrice X

IM Identitée de taille M

Produit de Kronecker

Re(.) Partie réelle

Im(.) Partie Imaginaire

1

2

INTRODUCTION GENERALE

Les techniques de transmissions numériques sans fil

connaissent depuis quelques années une grande révolution. Cette

révolution vient d'une part de la demande croissante en matière

de télécommunication et en matière d'échange de

données tout en bénéficiant des nouveaux services tels que

la télévision, la radio numérique, les réseaux

locaux sans fil, l'Internet à haut débit, la

téléphonie mobile et beaucoup d'autres applications

multimédias. D'autre part, les concepteurs des systèmes de

transmission sans fil cherchent à optimiser la qualité de service

et à surmonter les problèmes rencontrés lors de la

conception et de la mise en oeuvre de leurs systèmes.

La révolution en transmission numérique sans fil

se manifeste dans l'émergence de plusieurs nouvelles technologies

permettant d'augmenter considérablement les débits de

transmission et d'améliorer la qualité de transmission. Parmi ces

technologies, on a choisi pour notre étude la technologie MIMO (Multiple

Input Multiple Output) et la technologie MC-CDMA (Multi-Carrier Code Division

Multiple Access).

La technologie MIMO présente une solution prometteuse

pour augmenter l'efficacité spectrale et en transmettant les

données à travers un réseau multi-antennes en

émission et en réception. En effet, elle offre un débit

important et une bonne qualité de transmission grâce à la

diversité spatiale. Cependant, une source importante de

dégradation des performances dans les systèmes MIMO est la

sélectivité fréquentielle du canal. Les techniques

basées sur L'OFDM sont des solutions prometteuses pour combattre cette

sélectivité. En effet, la modulation OFDM transforme un canal

sélectif en fréquence en plusieurs sous-canaux non

sélectifs en fréquences.

La technique MC-CDMA correspond à la combinaison entre

la technique d'accès CDMA et la modulation OFDM où

l'étalement des données est effectué dans le domaine

fréquentiel. La technique d'accès CDMA permet à plusieurs

utilisateurs de partager le même canal radio en même temps et

à la même fréquence tout en assurant la séparation

de leurs données grâce à l'utilisation de codes

d'étalement orthogonaux.

L'objectif de ce projet de fin d'études est

d'étudier et d'implémenter un système sans fil utilisant

la technique MIMO associée à la technique MC-CDMA afin d'associer

les avantages de ces deux techniques dans un seul système qu'on

appellera MIMO-MC-CDMA.

On commence par évaluer les performances de la

chaîne MIMO-MC-CDMA en utilisant l'outil de

calcul et de simulation

Matlab. Ensuite, on propose une architecture des différentes composantes

de

toute la chaîne. Par ailleurs, cette chaîne est

implantée sur une architecture matérielle

reconfigurable à base de FPGAs afin de fournir les

résultats de synthèse au niveau RTL et d'évaluer les

performances de l'architecture proposée en termes de complexité

et de rapidité.

A TELNET, le développement des IPs reconfigurables et

réutilisables est basé sur une méthodologie de conception

basée sur une plateforme de prototypage sur une architecture cible

à base de FPGA de technologie Altera. D'ailleurs, la plateforme

matérielle et son outil de conception et de synthèse sont munis

d'une technique d'optimisation de performances du système grâce

à l'architecture des ressources internes du FPGA.

Dans le premier chapitre, on commencera par rappeler les

notions essentielles sur les systèmes de transmission numérique.

On rappellera également les caractéristiques du canal

radio-mobile. Puis, on présentera le principe de la modulation OFDM et

les principales techniques d'accès multiples utilisées dans les

systèmes de télécommunications. On s'intéressera

plus particulièrement à la technique d'accès CDMA pour

présenter par la suite la technique MC-CDMA.

Dans le deuxième chapitre, on présentera d'abord

les principales techniques de diversité. Puis, on présentera un

état de l'art des systèmes MIMO qui permettent d'exploiter la

diversité spatiale. On détaillera et on évaluera les

performances du multiplexage spatial qu'on a choisi pour la suite de notre

étude. Dans une dernière partie du chapitre, on étudiera

et on évaluera les performances de l'association de la technique du

multiplexage spatial et de la technique MC-CDMA.

Dans le troisième chapitre, on commencera par

présenter les principaux composants de l'architecture interne du circuit

FPGA cible Stratix.II.GX de la technologie Altera. Puis, on expliquera le flot

de conception et l'environnement de synthèse adopté dans les

conceptions matérielles. Ensuite, on s'intéressera à

décrire les architectures proposées des différents modules

du système MIMO-MCCDMA. Par ailleurs, on présentera les

résultats de synthèse niveau RTL et on analysera les performances

de l'architecture proposée en terme d'utilisation de ressources internes

et en termes de rapidité.

Finalement, les conclusions des différents travaux

effectués dans ce projet ainsi que quelques perspectives possibles

seront données dans un chapitre final.

3

4

5

6

Chapitre 1

La Technique MC-CDMA

1. Introduction

Pour développer les objectifs de ce projet de fin

d'études, on rappelle dans ce chapitre quelques notions essentielles

dans la communication numérique, les problèmes rencontrés

dans la transmission sur un canal radio, et les techniques utilisées

pour assurer une bonne qualité de transmission avec le minimum

d'erreur.

Tout d'abord, on rappelle dans ce chapitre les

différents éléments de base d'une chaîne de

transmission numérique. Puis, on présente les problèmes

généralement rencontrés dans les systèmes de

transmission radio-mobiles. Ensuite, on rappelle le principe de la modulation

OFDM permettant de transformer un canal sélectif en fréquence en

de multiples canaux non séléctifs en fréquence. On

rappelle également la technique d'accès multiple à

répartition par codes (CDMA) pour présenter par la suite la

technique qui combine entre la technique d'accès CDMA et la modulation

OFDM : la technique MC-CDMA.

2. Les composantes de base d'une chaîne de transmission

numérique

Les systèmes de transmission numériques

véhiculent de l'information (son, image, texte, ...) entre une source et

un destinataire. L'information transmise est représentée sous une

forme numérique afin de pouvoir la traiter dans les systèmes

numériques. A partir de la source, elle traverse un milieu appelé

canal de transmission pour atteindre le destinataire. Les canaux de

transmission utilisés dans les systèmes de transmission

numériques dépendent principalement de l'application de la

transmission à établir. En effet, un canal de transmission peut

être le câble, la fibre optique, le canal radioélectrique,

etc. Lors d'une transmission numérique, le canal introduit une

altération aux données transmises.

Dans cette partie, on décrit le fonctionnement d'une

chaîne de transmission numérique, de la source d'information

binaire au destinataire, par les étapes successives de codage, de

transmission dans un canal physique et de décodage. Comme on

privilège dans notre étude les transmissions hertziennes, on ne

présentera que les canaux à évanouissements.

La figure 1.1 résume l'ensemble des composantes de base

d'une chaîne de transmission numérique.

Figure 1.1. Composantes de base d'une chaîne de

transmission

2.1. Le codeur et le décodeur de canal

Le rôle principal du codeur et du décodeur de

canal est de minimiser les erreurs introduites par le canal de transmission. Le

codeur de canal utilisé à l'émission ajoute aux

informations numériques à transmettre des bits de redondances

pour permettre au récepteur de détecter et corriger les erreurs

de la transmission.

A la réception, le décodeur de canal doit avoir

la structure adaptée au codeur de canal utilisé à

l'émission. Il doit aussi comporter un caractère correcteur

d'erreur permettent de retrouver les données transmises avant le codage

avec le minimum d'erreurs.

Dans ce travail, on a choisi d'utiliser comme codeur de canal

le codeur convolutif. En effet, ce codeur est le plus utilisé dans les

systèmes de télécommunication mobiles. Le principe de ce

codeur consiste à calculer chaque bloc de n éléments

binaires en sortie en fonction de k éléments présents

à son entrée et des m blocs présents

précédemment. La quantité m+1 s'appelle longueur de

contrainte du codeur [2]. La figure 1.2 illustre un codeur convolutif avec une

entrée k=1, 2 sorties n=2 et de longueur de contrainte m+1=3. Le

rendement de ce codeur défini par k/n est égal à1/2.

Figure 1.2. Codeur convolutif (k=1,n=3 et (m+1)=3)

Les sorties de ce codeur s'écrivent en fonction des bits

d'entrée comme suit :

s1 n = bn + bn-1 + bn-2 , (1.1)

et

s2 n = bn + bn-1 . (1.2)

Les calculs se font en modulo 2. Les bits bn-1

et bn-2 sont stockés dans les registres à

décalages du codeur.

A la réception, on décode les séquences

reçues par l'algorithme de viterbi. Cet algorithme prend à

l'entrée les bits issus du bloc de démodulation. En utilisant un

treillis construit à partir des paramètres du codeur convolutif,

le décodeur cherche la séquence binaire la plus vraisemblable

(c'est-à-dire il minimise la distance euclidienne entre le signal

reçu et le signal supposé émis d'information).

2.2. La modulation/démodulation numérique

La composante de la modulation numérique consiste

à étiqueter les symboles avec les bits d'information. Supposons

que chaque mot-code contient m bits, alors le débit de symboles

Ds est alors égal à :

1

Ds =

m

Db , (1.3)

où Db est le débit des éléments

binaires.

La modulation de chaque mot-code de m bits peut

générer M=2m symboles différents. L'ensemble de

ces symboles forme une constellation caractéristique en fonction de la

modulation utilisée.

Au bloc de démodulation, le symbole reçu est

altéré par l'évanouissement du canal et du bruit. Son

processus de quantification consiste donc à partitionner la

constellation du modulateur en des zones de décision. Les seuils de ces

zones sont indiqués par des traits discontinus dans les figures qui

présenteront les trois principaux types de modulation (figure 1.3, 1.5

et 1.6)

2.2.1. Modulation à déplacement d'amplitude ASK

(Amplitude Shift Keying)

La constellation de la modulation ASK est une droite qui

contient M points répartis de la manière

illustrée dans

la figure 1.3. La répartition des mots-codes sur une constellation M-ASK

est souhaitable

qu'elle soit de telle sorte qu'il y a une différence

d'un seul bit entre deux mots codes voisins. Cette répartition est

semblable au codage de Grey. Par exemple, la constellation d'une modulation

8-ASK est représentée dans la figure 1.4.

Figure 1.3. Constellation de la modulation M-ASK

Figure 1.4. Constellation de la modulation 8-ASK

2.2.2. Modulation à déplacement de phase PSK (Phase

Shift Keying)

(2 1)

k

La constellation de la modulation M-PSK est un cercle de rayon A

qui contient M points répartis de la manière suivante :

0

ck A e

. M , (1.4)

pour k=0, 1, ..., M-1, où 0 est la phase du

premier symbole de la constellation.

Les symboles obtenus d'une modulation PSK sont des symboles

complexes de mêmes modules mais de phases différentes. La figure

1.5 illustre les modulations 2-PSK, 4-PSK et 8-PSK en utilisant le codage de

Gray pour assigner les mots-codes aux symboles.

2.2.3. Modulation d'amplitude en quadrature QAM (Quadrature

Amplitude Modulation)

La constellation de la modulation QAM se compose de deux axes

dont le premier désigne la partie réelle du symbole et le second

désigne sa partie imaginaire. Chaque axe est semblable à une

modulation ASK de mots-codes de m bits. Alors, la constellation formée

par les deux axes est un modulateurs de mots-codes de 2m bits. Le symbole

délivré d'un modulateur est de la forme :

ckakj.bk, (1.5)

où ak et bk sont obtenus des alphabets {#177;1, #177;3,

..., #177;(M-1)} avec M=2m.

Un exemple de constellation M-QAM, avec M=16, est

présenté dans la figure 1.6.

7

Figure 1.5. Constellation des modulations BPSK, QPSK et

8-PSK

Figure 1.6. Constellation de 16-QAM utilisant le codage de Grey

C'est la modulation QAM qu'on a choisie pour la suite de notre étude.

3. Le canal radio-mobile

3.1. Effet multi-trajet d'un canal radio

Lors d'une transmission à travers un canal radio entre

un émetteur et un récepteur, le signal émis se propage

dans plusieurs directions du milieu radio et parvient au récepteur sur

des chemins différents [3]. En effet, au moment de la propagation du

signal, des phénomènes impliquant la multiplicité des

chemins interviennent généralement sous trois formes :

- La réflexion : lorsque l'onde

électromagnétique du signal rencontre dans sa direction une

surface lisse dont les dimensions sont grandes par rapport

à la longueur d'onde du signal.

- La diffusion : lorsque l'onde électromagnétique

du signal entre en collision avec une surface

dont les dimensions sont de l'ordre de la longueur d'onde du

signal. Ce phénomène engendre la diffusion de l'onde dans

plusieurs directions.

- La diffraction : lorsque l'onde électromagnétique

heurte une arête d'un corps volumineux

dont les dimensions sont grandes par rapport à la longueur

d'onde du signal. Ce phénomène cause l'apparition d'ondes

secondaires.

Ces phénomènes sont représentés dans

la figure 1.7.

Figure 1.7. Modélisation du phénomène de

trajets multiples

L'avantage de ce phénomène de propagation

multi-trajets est qu'il assure une certaine continuité de la couverture

radio en permettant la communication dans le cas où l'émetteur et

le récepteur ne sont pas en vue directe. Néanmoins, cette

multiplicité de trajets engendre des difficultés au niveau du

récepteur. En fait, le signal reçu est une combinaison de

plusieurs répliques du signal émis avec des amplitudes, des

phases et des temps d'arrivées différents.

Les évanouissements d'un canal multi-trajets sont

classifiés en trois types :

- Les évanouissements à grande échelle : ils

traduisent l'atténuation de la puissance du signal

en fonction de la distance qui sépare l'émetteur du

récepteur.

- Les évanouissements à moyenne échelle :

ils traduisent l'atténuation du signal transmis à

cause des obstacles rencontrés. Ces

évanouissements sont appelés aussi l'effet de masques.

- Les évanouissements à petite échelle : ils

traduisent le changement rapide de l'amplitude et

de la phase du signal reçu causé par l'addition

constructive ou destructive des interférences sur les différents

trajets.

3.2. Etalement temporel

On a vu que dans un système radio-mobile, le

récepteur reçoit le signal émis sur plusieurs

répliques

avec des retards différents. L'étalement

temporel Tm est le temps qui sépare l'arrivée du

premier

trajet de l'arrivée du dernier trajet [4]. Son inverse est en

général du même ordre que la bande de

|

cohérence du canal :

|

1

T m

|

~ , sachant que la bande de cohérence d'un canal

Bc correspond à la

B c

|

9

gamme de fréquences sur laquelle les amplitudes des

composantes fréquentielles du signal subissent des atténuations

semblables.

Soit Bs la largeur de la bande du signal transmis. Si

Bs « B c alors toutes les amplitudes des

composantes fréquentielles du signal transmis subissent

des atténuations semblables. Dans ce cas, le canal est dit non

sélectif en fréquence. Dans le cas contraire, les amplitudes des

composantes fréquentielles du signal subissent des atténuations

différentes, et le canal est dit sélectif en fréquence et

on a un phénomène d'interférences entre symboles. Pour

éviter ce problème d'interférences entre les symboles, on

essaie en pratique de rendre la largeur de bande du signal très petite

par rapport à la bande de cohérence du canal.

3.3. Etalement fréquentiel : effet Doppler

Dans le cas où l'émetteur et le récepteur

sont en mouvement relatif avec une vitesse radiale y constante, la

fréquence du signal reçu subit un décalage constant

proportionnel à cette vitesse y et à la fréquence

porteuse: il s'agit de l'effet Doppler [4]. L'étalement

fréquentiel fd est la différence entre le plus grand et le plus

petit décalage en fréquence des différents trajets. Son

inverse est en

général du même ordre que le temps de

cohérence du canal : f 1 ~, sachant que le temps de

T c

d

cohérence d'un canal Tc est la durée

pendant laquelle le canal ne varie pas (c'est-à-dire que les distorsions

temporelles du canal sont négligeables).

Si le temps de cohérence d'un canal est très grand

par rapport au temps d'un symbole émis, le canal est dit à

évanouissements lents. Dans le cas contraire, le canal est dit à

évanouissements rapides.

Ainsi, pour que le canal soit non sélectif en

fréquence et à évanouissements lents, il faut que la

durée des symboles émis vérifie la relation suivante :

T m « T s « T c , (1.6)

où Ts est la durée de transmission d'un

symbole.

3.4. Modélisation du canal à évanouissements

lents

On considère dans la suite de l'étude que le

canal subit des évanouissements lents. Le signal équivalent en

bande de base reçu à la sortie de ce canal comportant N trajets

multiples s'exprime alors par :

N 1

r t

( )( ) ( ) (1.7)

n n

s t b t ,

n 0

où b(t) est le bruit blanc additif gaussien (BBAG)

complexe de variance N0, et n et n désignent

respectivement l'atténuation complexe et le retard du signal pour chaque

trajet n, n=0, 1, ..., N-1.

Le nombre de trajets N emprunté par un même

signal est généralement énorme. Le théorème

de la limite centrale permet de regrouper les N trajets en L paquets [5].

Chaque paquet a une atténuation complexe résultante l

et un retard moyen l. L'expression du signal reçu devient alors :

L 1

r t

( )( ) ( ) . (1.8)

l l

s t b t

l 0

1

Ainsi, le signal échantillonné au rythme symbole

reçu à l'instant k s'écrit :

TS

L 1

r r kT

( ) l (1.9)

k S l k k

s b

l 0

L'atténuation complexe lpeut être exprimée

par un module et une phase comme suit :

l hle i l, (1.10)

où l est une variable aléatoire de

loi uniforme sur [0,2] et hl est une variable aléatoire qui suit la loi

de Rayleigh dans le cas où on considère qu'il n'y a pas un trajet

direct entre l'émetteur et le récepteur. Si on considère

qu'il y a un trajet direct entre l'émetteur et le récepteur, hl

suit alors la loi de Rice [1].

On rappelle que les densités de probabilité des

lois de Rayleigh et de Rice sont de la forme :

x 2

x 2

p x e

( ) 2 2 , (1.11)

Rayleigh

10

x22

|

et

|

x x

2

p x e I

( ) 2 0 ( 2 )

2

Rioe

|

, (1.12)

|

où 2 est la variance de hl, est un

paramètre de non-centralité dû au trajet direct et I0(x)

est la fonction de Bessel modifiée d'ordre 0.

4. La modulation OFDM

Pour une transmission numérique mono-porteuse, la

transmission d'un symbole ne pourrait être parfaite (sans

interférences entre symboles) que si :

Tm« Ts . (1.13)

D'où, pour une transmission mono-porteuse, le débit

de transmission est limité par le délai de propagation dans le

canal [6].

Pour surmonter ce problème, la modulation OFDM intervient

comme une technique simple et efficace pour améliorer le débit de

transmission tout en évitant l'interférence entre symboles.

L'idée de la modulation OFDM est de subdiviser la bande

de transmission en plusieurs sous canaux qui permettent la transmission en

parallèle. Les données sont converties en sous-flux

parallèles dans le but de les moduler sur des sous-porteuses

correspondantes aux sous-canaux à bande réduite.

4.1. Principe de l'OFDM

Soit une séquence de Lc symboles xn,

n=0, 1, ..., Lc-1. Chaque symbole xn module un signal

à fréquence fn. Soit T0 la durée d'un symbole

OFDM. Le signal OFDM, pendant l'intervalle [0, T0[ s'écrit :

L c 1

|

où

|

s(t)=

|

n

|

0

|

2 . .

j n f t

x e n ,

n

|

(1.14)

|

fn = f0+n. F (1.15)

avec F est l'espacement entre deux fréquences voisines.

|

1

2 j n t

T

Si F=1/T0 alors le produit scalaire de 0

e

|

1

2 j k t

avec T 0

edonne :

|

1 1 1 1

j n t j k t T j n t j k t j n k t

1 1 1

2 2 T 2 ( ) T si n k

1

2 2

(1.16)

0 T T 0

0 0 0 0 e dt

0

e e

T T

, e e dt

T0 T0 0 si n k

0 0

11

D'où le multiplexage des symboles est orthogonal si :

F=1/T0.

Le signal s(t) s'écrit alors :

L c j

1 2

s(t)= 0 0

e x e

2 j f t T

n

. (1.17)

nt

Lc

T 0

n 0

En terme de débit, l'OFDM est équivalent à

une modulation mono-porteuse utilisant la bande W=

|

et une durée symbole T1= T 0

L c

|

. L'avantage de l'OFDM par rapport à la modulation

mono-porteuse est

|

qu'elle est beaucoup moins sensible pour un canal

sélectif en fréquence [6] puisqu'elle consiste à envoyer

les symboles sur des sous-canaux de largeur F au lieu d'envoyer sur une bande

de largeur W.

4.2. Modulation par la Transformée de Fourier

Discrète DFT

La modulation OFDM peut être implémentée

aisément. En effet, lorsqu'on échantillonne le signal OFDM s(t)

à la cadence d'échantillonnage Te= T0/Lc,

on obtient l'écriture suivante :

|

sk=s(kTe)=

|

nk

L j

1 2

c

L c

x e , pour k=0,1,...,Lc-1. (1.18)

n

|

n 0

Cette expression correspond à la Transformée de

Fourier Discrète Inverse (IDFT) d'ordre Lc de la

séquence de symboles xn [7].

La démodulation est effectuée par une

transformée de Fourier discrète (DFT) :

nk

N j

1 2

L c

s e (1.19)

n

L 0

ck=DFT{s(n)}=

1

cn

12

4.3. Introduction de l'intervalle de garde en OFDM

Généralement, dans une transmission OFDM, le

canal est dispersif et son effet mémoire gène la transmission. En

effet, ce phénomène cause l'interférence entre les

symboles. Pour cela, chaque symbole OFDM est prolongé par un intervalle

de garde appelé aussi "extension cyclique".

L'extension cyclique consiste à répéter au

début d'un symbole OFDM de taille Lc, les L dernières

symboles du bloc [7]. D'où la taille du symbole OFDM devient

égale à Lc+L symboles.

La longueur de l'intervalle de garde doit être plus grande

que le plus grand des retards du canal. Dans la plupart des cas, L est pris

égal à Lc/4.

13

Les symboles OFDM émis sont représentés

selon le schéma de la figure 1.8.

Figure 1.8. Introduction de l'intervalle de garde au symbole

OFDM transmis

En réception, l'intervalle de garde de chaque bloc

reçu est écarté afin de récupérer le bloc

contenant les Lc symboles désirés pour les traiter

dans les différentes composantes de la chaîne de

réception.

L'expression du symbole OFDM reçu est égale

à :

|

rk=

|

nk

L j

1 2

c

hxe b

L c , (1.20)

n n n

|

n0

où hn est la réponse

fréquentielle du canal relative à la nième

sous-porteuse ~,, et bn est un BBAG introduit au symbole OFDM pour

la nième sous-porteuse. D'où la démodulation de

ce symbole est obtenue par le calcul de la DFT de rk. Ainsi, on peut constater

qu'une chaîne d'émission et de réception d'un

système OFDM peut être représentée par le

schéma de la figure 1.9.

Figure 1.9. Chaîne d'émission et de

réception du modulateur OFDM

5. Les techniques d'accès multiple

L'objectif des communications mobiles est de permettre la

connexion d'un grand nombre d'utilisateurs au canal et par suite à

l'infrastructure du réseau. Pour cela, il existe des techniques

d'accès multiples à travers lesquels un grand nombre

d'utilisateurs partagent un canal de communication commun pour transmettre

leurs informations au récepteur. Ces techniques se basent

essentiellement sur la séparation des signaux des différents

utilisateurs.

Trois techniques d'accès multiples sont

généralement employées dans les systèmes de

communication [8].

5.1. Accès multiple à répartition par

temps

Dans la technique TDMA (Time Division Multiple Access), le

temps est divisé en trames (figure1.10). Chaque trame est divisée

en time slots (TS). Dans chaque timeslot, un utilisateur peut transmettre ses

données. Donc, n utilisateurs peuvent transmettre leurs données

pendant une trame. L'avantage de cette technique est que plusieurs utilisateurs

peuvent communiquer utilisant une seule bande de fréquence.

5.2. Accès multiple à répartition par

fréquence

Dans la technique FDMA (Frequency Division Multiple Access),

la bande accessible au canal est divisée en sous-bandes (figure 1.11).

Chaque utilisateur utilise une sous-bande pour transmettre ses données.

L'avantage de cette technique réside dans la possibilité de

plusieurs utilisateurs d'entrer en communication en même temps mais en

utilisant des sous bandes différentes.

5.3. Accès multiple à répartition par

code

Dans la technique CDMA (Code Division Multiple Access), chaque

utilisateur possède un code unique par lequel ses informations son

codées. La séparation des utilisateurs est donc assurée

par la distinction de leurs codes utilisés. L'avantage de la technique

CDMA est qu'elle permet la communication des différents utilisateurs au

même temps et à la même fréquence (figure 1.12).

Figure 1.10. La technique TDMA

Figure 1.11. La technique FDMA

Figure 1.12. La technique CDMA

14

Dans la suite du projet de fin d'études, on adoptera la

technique CDMA dans l'étude et dans l'implémentation car cette

technique présente une complexité d'implémentation plus

simple par rapport aux techniques TDMA et FDMA. De même, cette technique

simplifie la planification du partage du canal.

15

6. La technique CDMA

L'accès multiple à répartition par code

ou CDMA est une technique qui permet à plusieurs d'utiliser utilisent la

même bande de fréquence en même temps.

L'élément principal du CDMA est la technique d'étalement

du spectre qui transforme un signal en bande étroite en un signal

à bande plus large que celle nécessaire au transfert de

données [6].

6.1. Principe du CDMA

Dans un système CDMA, le signal provenant de chaque

utilisateur est étalé par son propre code d'étalement puis

transmis à travers le canal radio. A la réception, le signal

reçu est désétalé par le même code

d'étalement utilisé à l'émission afin de

récupérer les données initialement transmises.

La technique d'étalement en CDMA est utilisée

par différentes méthodes. Les méthodes les plus

généralement utilisées sont : DS-CDMA et FH-CDMA. On

s'intéresse dans ce projet à l'étalement par

séquences directes DS-CDMA. La figure 1.13 montre un exemple

d'étalement par séquence directe (DS-CDMA). Il s'effectue par un

produit entre le signal en bande de base et une séquence

d'étalement 8 fois plus rapide que le flot de données.

Figure 1.13. Etalement par séquences directes

Soit

Ts la durée d'un symbole de données et Tc

la durée d'un chip de la séquence d'étalement. Le

|

rapport N= T s

T c

|

est appelé le facteur d'étalement car d'une part

il s'agit de la multiplication du signal

|

par le code d'étalement. D'autre part, la bande du

signal étalé est élargie d'un rapport égal au

facteur d'étalement par rapport au signal non étalé.

Les codes d'étalement utilisés en CDMA, sont

choisis en fonction de la situation et de l'application appropriées du

système. Il existe plusieurs codes qui sont utilisés dans les

systèmes de télécommunication utilisant la technique CDMA,

tels que les codes de Walsh-Hadamard, les codes Gold, les codes Kasami, les

codes Barker, etc [6]. Dans cette étude, on n'utilisera que les

séquences

H H

de Walsh Hadamard. Ces codes sont obtenus d'après la

matrice de Hadamard qui, pour un ordre N, s'écrit par la relation

récursive suivante :

HN

N N

2 2

(1.21)

H H

2 2

N N

sachant que H1 = 1.

|

Par exemple, la matrice de Hadamard à l'ordre 4

s'écrit :

1 1 1 1

1 1 1 1

H 4 1 1 1 1

1 1 1 1

|

(1.22)

|

On peut diviser les codes par un facteur de normalisation qui est

fonction de leurs longueurs. On obtient les colonnes d'étalement

relatives à la matrice CN tel que

1

CN=

N

H . (1.23)

N

16

L'avantage majeur des codes de Walsh-Hadamard est que les codes

sont deux à deux orthogonaux :

( ) ( ) 1

i j si ij

c c (1.24)

,

0 sinon

6.2. Modélisation du système CDMA

On suppose qu'on a Nu utilisateurs qui vont envoyer

leurs données en utilisant la même ressource

radio. Soit ( i )

dk le kéme symbole émis par

l'utilisateur i. Chaque symbole émis par l'utilisateur i au

débit Ts à l'instant k est

étalé en utilisant une séquence

c(i)=(c(i)(0), ..., c(i)(N-1)). Cette

séquence est émise à un rythme chip 1/Tc. Pour

le cas d'un utilisateur i, le signal émis au rythme chip 1/Tc

s'écrit alors :

|

x n k

( ) ( ) ( )

i i i

c n d k

,

|

, pour n=0,...,N-1. (1.25)

|

Le signal reçu échantillonné au rythme chip

1/Tc est donné par :

N u

1 N 1

u

r hxb h c d b

( ) ( ) ( ) ( ) ( )

i i i i i

n k n k n k n k n k n k n k , (1.26)

, , , , , ,

i0 i0

17

où bn,k est un bruit BBAG complexe de variance

N0 et ( )

h n k le coefficient du canal relatif à l'utilisateur

i.

i

,

Dans un canal radio-mobile, l'interférence

d'accès multiple limite la capacité du système CDMA. Ce

problème a donné naissance à plusieurs travaux de

recherches évoqués sous le nom "Détection

multi-utilisateurs" [7]. Cette méthode de détection sera

développée dans le paragraphe suivant lorsqu'on associe la

technique CDMA à la modulation OFDM.

7. La technique CDMA associée à la modulation

multiporteuses

Plusieurs techniques ont été

réalisées dans la littérature pour associer l'OFDM comme

technique de modulation et le CDMA comme technique d'accès permettant

d'obtenir de très bonnes performances dans le cas de transmissions sur

des canaux sélectifs en fréquence. En effet, cette association

permet de tirer profit de la robustesse et de l'efficacité spectrale de

la modulation OFDM tout en bénéficiant de la souplesse offerte

par l'accès multiple à répartition par code. Parmi les

techniques, on peut citer MC-DS-CDMA [9], MT-CDMA [10] et MC-CDMA [11]-[12].

Dans les schémas MT-CDMA et MC-DS-CDMA,

l'étalement est effectué dans le domaine temporel. Par contre,

dans la technique MC-CDMA, au lieu d'appliquer les séquences

d'étalement dans le domaine temporel, on les applique dans le domaine

fréquentiel en projetant chaque élément (chip) de la

séquence d'étalement à une sous-porteuse OFDM à un

débit identique au débit initial des données avant

étalement.

Prasad et Hara montrent que la technique MC-CDMA est la plus

performante sur liaison descendante [13]. Cela justifie notre choix de cette

technique pour l'association de l'OFDM et du CDMA.

Dans la suite, on notera Nu le nombre d'utilisateurs

et N la longueur des codes d'étalement.

7.1. Partie émettrice

Les données de chaque utilisateur i sont

étalées par le code d'étalement qui lui correspond. Les

symboles étalés alimentent par la suite la modulation OFDM

(figure 1.14). Le nombre de sous- porteuses de la modulation est

généralement égal à un multiple de longueur N des

codes d'étalement. On suppose dans notre étude que ce nombre est

égal à Lc=N. L'étalement de la donnée

dk relative au iième utilisateur par

le code d'étalement c(i) engendre la séquence suivante

:

( i )

x n k

( ) ( ) ( )

i i i

c n d k , pour 0=n= Lc-1. (1.27)

,

18

Figure 1.14. Circuit d'émission pour un utilisateur de

la technique MC-CDMA

Cette séquence est introduite dans le modulateur OFDM

comportant Lc sous-porteuses. D'après le paragraphe 4.2, le

kème échantillon du symbole OFDM obtenu relatif au

iième utilisateur s'exprime par :

L nk

1 2

c j

s xe

( ) ( )

i L

i c, 0=k= Lc-1. (1.28)

k n k

,

n0

En remplaçant, ( )

x n k par son expression (1.27), on obtient :

i

,

L12 nk c j

s c d e

( ) ( ) ( )

i i i L c, pour 0=k= Lc-1 (1.29)

k n k

n 0

Dans le cas où les Nu données des

Nu utilisateurs sont émises simultanément, elle sont

étalées de la manière suivante :

u

x c d

( ) ( )

i i , pour 0=n= Lc-1. (1.30)

n k n k

,

i 1

Cette équation peut être mise sous une forme

matricielle comme suit :

xk=C.dk (1.31)

où xk=[x0,k, ..., xLc-1,k]T, dk=[

(0)

dk , ..., ( u 1 )

dk ]T le vecteur de symboles complexes, et

C=[c(0), ..., c(Nu-1)]

est la matrice des codes d'étalement des utilisateurs de

taille LcxNu avec c(i) est le code d'étalement

propre au iième utilisateur.

Après étalement, la séquence xk est

passée par la modulation OFDM. Le symbole modulé obtenu est :

L j L ~ nk

1 2 1 1

nk

c c u 2 j

s x e c d e

L ( ) ( )

i i L

c c , pour 0=k=Lc-1 (1.32)

k n k

, n k

n n i

0 0 0

19

7.2. Partie réceptrice

On suppose que le nombre de sous-porteuses est suffisamment

grand pour pouvoir supposer que le canal est constant pendant la durée

d'un symbole OFDM. On peut considérer également que le canal de

chaque sous-porteuse est plat et donc que l'interférence entre symboles

est supprimée par un choix adéquat de l'intervalle de garde

(paragraphe 4.3). L'évanouissement du canal au niveau de chaque

sous-porteuse n peut alors être modélisé par un gain

complexe hn.

Au niveau du récepteur, le kème symbole

reçu au niveau de la nième sous-porteuse est de la

forme :

Nu1 Nu1

r h xb h d c b h x b

( )

i ( ) ( )

i i

n k n n k n k n k n n k n n k n k , pour n=0,...,Lc-1

(1.33)

, , , , , ,

i

0 i0

où hn et bn sont respectivement la

réponse du canal et le bruit complexe BBAG au niveau de la nième

sous-porteuse.

Le vecteur des symboles reçus r de longueur Lc

sur les Lc sous-porteuses est donné par :

|

N 1

u

h x ( )

i

0 0, k

r b h x b

? 0

0, 0

k i 0, 0

k 0, 0,

k k

? ? ? ? ? ? ? ?

N 1

u

r L k

1, ( ) 1 1, 1,

0 ?

L k

1,

c c c c c

h x i L L k L k

b h x b

L L k

c c

1 1,

i0

|

. (1.34)

|

Ce qui donne alors :

rk=H.xk+bk, (1.35)

où rk=[r0,k, ..., rLc-1,k] T est le vecteur

des symboles reçus de longueur Lc, H=diag(hn ;

0=n= Lc-1) est une matrice diagonale de taille

LcxLc, chaque élément de la diagonale

hn correspond à la réponse fréquentielle du

canal pour chaque sous-porteuse, bk=[b0,k, ..., bLc-1,k]T

est le vecteur bruit complexe BBAG sur les Lc porteuses.

La détection des données du ième

utilisateur se fait comme suit :

Lc

à

1

d cg r

( ) ( )

i i

k n n n k , (1.36)

,

n 0

où gn est l'inverse du gain du canal

estimé pour la nème sous-porteuse.

Plusieurs méthodes ont été

proposées dans la littérature pour déterminer les

coefficients gn [7]. On présente dans le paragraphe suivant

les techniques de détection mono-utilisateur, i.e. aucune connaissance

des codes d'étalement des autres utilisateurs n'est nécessaire.

Nous présentons également le principe de la détection

multi-utilisateurs.

Figure 1.15. Circuit de réception pour un utilisateur de

la technique MC-CDMA

7.3. Les techniques de détection en MC-CDMA

Dans ce paragraphe, on présente des techniques de

détection possibles en MC-CDMA. 7.3.1. Détection

mono-utilisateur

Au niveau du récepteur, la donnée du

iième utilisateur est détectée

indépendamment des données des autres utilisateurs. On rappelle

que la décision sur le kème symbole du

ième utilisateur se fait de la manière suivante :

Lc

à

1

d c g r

( ) ( )

i i (1.37)

k n n n k

,

n 0

Les méthodes généralement utilisées

pour le calcul de gn dans le cas d'une détection

monoutilisateur sont :

- Egalisation avec critère de forçage à

zéro (ZF) :

*

2

hn

hn

(1.38)

g n

1

h L

*

n c

2

(1.39)

g n

hn

N SNR

u

20

- Egalisation avec critère de minimisation de l'erreur

quadratique moyenne (MMSE) :

21

22

où d

S~Rest le rapport signal su bruit qui est défini par le

rapport de la variance du signal sur la

2 n

variance du bruit.

à

Les équations (1.38) et (1.39) montrent que le canal doit

être estimé pour chaque sous-porteuse. Les équations (1.37)

pour i=0,1, ..., Nu-1 peuvent être écrites sous la

forme matricielle suivante :

d C G.r (1.40)

T

k k

T

où à à ( 0) ,..., à ( u

1)

d , rk=[r0,k, ..., rLc-1,k]T, C est la

matrice d'étalement et G=diag(gn ; 0=n=Lc-1)

d k d k ~

k

est la matrice d'égalisation mono-utilisateur utilisant

l'un des critères d'égalisation ZF ou MMSE. 7.3.2.

Détection multi-utilisateurs

Dans ce cas, toutes les données de tous les

utilisateurs sont détectées conjointement. La technique de

détection se base sur la minimisation de la distance euclidienne du

signal reçu des données estimées. On rappelle que le

kème symbole reçu sur les Lc sous-porteuses

s'écrit (1.40) :

rk=HCdk+bk (1.41)

Dans le cas d'une égalisation et d'un

désétalement conjoint, l'égaliseur selon le critère

ZF minimise

|

l'erreur quadratique (rk-HC

|

à dk )T(rk-HC

|

à

dk). La sortie de cet égaliseur est donc

donnée par :

|

T † T †

1

F C H HC C H ZF(1.42)

L'égaliseur selon le critère MMSE minimise l'erreur

quadratique moyenne E[( à dk-dk)T( à

dk-dk)] :

1

1

F C H HC C H

T † T †

MMSE SNR(1.43)

à

Ainsi le vecteur dk correspondant aux symboles

égalisés et désétalés de tous les

utilisateurs est

donnée par :

à

dk=F.rk (1.44)

On note que les expressions des égaliseurs ZF et MMSE

seront données plus en détail dans le chapitre suivant lors de

l'association du système MIMO et de la technique MC-CDMA.

8. Conclusion

Dans ce chapitre, on a d'abord décrit les composantes

de base d'une chaîne de transmission numérique. Puis, on a

présenté les caractéristiques du canal de transmission

radio-mobile. On a présenté par la suite la modulation OFDM dont

le but est d'augmenter le débit de transmission en garantissant une

transmission dans des sous-canaux non sélectifs en fréquences.

Ensuite, on a présenté les principales techniques d'accès

multiples permettant le partage de l'espace des canaux de transmission. On a

fixé notre choix sur la technique CDMA puisqu'elle permet une

transmission de données de plusieurs utilisateurs en même temps et

sur la même fréquence. Par ailleurs, on a présenté

la technique qui associe la modulation OFDM à la technique CDMA.

Dans la suite de ce travail, on va étudier et

implémenter une architecture qui combine entre la technique MC-CDMA et

la technique multi-antennes, dans le but d'améliorer davantage les

performances et la qualité de la transmission.

23

Chapitre 2

Multiplexage spatial dans un contexte MC-CDMA

1. Introduction

Depuis une dizaine d'années, une nouvelle technologie

est apparue dans les systèmes de télécommunication qui

permet d'améliorer la qualité de transmission. Cette technologie

a comme principaux objectifs d'augmenter le débit de transmission et

d'exploiter la diversité offerte par le système. Il s'agit du

système à entrées multiples et à sorties multiples

(appelé aussi MIMO) qui emploi plusieurs antennes en émission et

plusieurs antennes en réception. La plupart des études sur les

systèmes MIMO considèrent un canal non sélectif en

fréquence. Cependant, l'effet multi-trajets provoque la

sélectivité fréquentielle du canal. Pour cette raison, on

se propose dans ce chapitre d'étudier l'association de la technique

MC-CDMA à la technique MIMO puisque la technique MCCDMA permet d'une

part l'accès de plusieurs utilisateurs dans le même canal radio.

D'autre part, le MC-CDMA permet une transmission dans un canal non

sélectif en fréquence grâce à la modulation OFDM

employée.

Dans ce chapitre, on commence tout d'abord par définir

la notion de la diversité et rappeler les différentes techniques

de diversité. On s'intéresse par la suite à l'étude

du système MIMO en introduisant deux approches possibles à

l'émission : le codage spatio-temporel et le multiplexage spatial.

Ensuite, on focalise sur la technique du multiplexage spatial et on

évalue ses performances en fonction de la technique de détection

utilisée à la réception. Dans la deuxième partie de

ce chapitre, on présente une architecture permettant l'association de la

technique multiplexage spatial à la technique MC-CDMA. On évalue

également les performances de cette nouvelle chaîne.

2. Techniques de diversité

La diversité est une technique utilisée dans les

systèmes de transmissions radio-mobiles afin de lutter contre

l'évanouissement causé par les trajets multiples du canal de

transmission. Elle consiste à recevoir plusieurs répliques du

signal émis affectés par des évanouissements

indépendants. L'ordre de diversité est égal au nombre de

voies indépendantes à la réception [1]-[4].

Les principales formes de diversité sont la

diversité temporelle, la diversité fréquentielle et la

diversité spatiale.

2.1. Diversité temporelle

Cette diversité consiste à envoyer plusieurs

répliques du signal à transmettre dans des intervalles de temps

séparés d'au moins le temps de cohérence du canal

Tc afin d'assurer un bonne décorrélation des signaux

(figure 2.1). Cette diversité est intéressante pour le cas de

transmissions dans un canal sélectif en temps.

Figure 2.1. Emission du même signal à des instants

séparés par le temps de cohérence du canal

2.2. Diversité fréquentielle

La diversité fréquentielle consiste à

envoyer plusieurs répliques du même signal à transmettre

sur des fréquences différentes séparées d'au moins

la bande de cohérence du canal Bc (figure 2.2). Elle est

intéressante pour les cas des transmissions dans un canal

sélectif en fréquence. Cette diversité est

généralement utilisée dans les systèmes OFDM.

24

Figure 2.2. Emission du même signal sur des

fréquences différentes

2.3. Diversité spatiale

La diversité spatiale consiste à envoyer ou

recevoir le signal sur des antennes différentes espacées par une

distance plus grande que la distance de cohérence. Cette distance est la

séparation minimale des antennes garantissant des évanouissements

indépendants.

25

Figure 2.3. Diversité spatiale à l'émission

Figure 2.4. Diversité spatiale à la réception

Les diversités temporelles, fréquentielles et

spatiales à l'émission diminuent l'efficacité spectrale du

système puisqu'elles nécessitent la répétition du

même signal. En associant un codage correcteur d'erreurs avec l'une des

ces techniques de diversité, on augmente l'efficacité spectrale

et on évite le gaspillage des ressources spectrales.

On note également que la combinaison de plusieurs

techniques de diversité permet de mieux combattre les effets

d'évanouissement du canal.

On présente dans le paragraphe suivant les

systèmes multi-antennes (MIMO) qui associent plusieurs antennes à

l'émission et à la réception. Cela permettra par la suite

de proposer une architecture pour l'implémentation d'un système

MIMO dans un contexte MC-CDMA.

3. Les systèmes MIMO

Un système MIMO est un système qui comporte

plusieurs antennes à l'émission et plusieurs antennes à la

réception. Les deux principaux avantages des systèmes MIMO sont

d'offrir une diversité spatiale à l'émission et à

la réception, et d'augmenter le débit de transmission des

données.

Soit un système MIMO comportant Nt antennes

d'émission et Nr antennes de réception (figure 2.5).

On suppose que la bande de fréquence utilisée pour la

transmission est assez étroite pour que le canal soit non

sélectif en fréquence. Chaque trajet entre une antenne

émettrice t et une antenne réceptrice r est

modélisé par un gain complexe hrt(k)

représentant l'évanouissement du trajet. A la réception,

chaque antenne reçoit la somme des symboles xt transmis

simultanément par chacune des Nt antennes émettrices. Le signal

yr reçu par la rième antenne à

l'instant k peut alors s'écrire :

Nt

|

yr

|

( ) ( ) ( ) ( )

k h k x k b k

rt t r

|

, (2.1)

|

t 1

où br(k) représente le bruit complexe

qui perturbe le signal reçu sur la rième antenne de

réception à l'instant k, modélisé par un Bruit

BBAG.

Figure 2.5. Représentation des différents trajets

entre antennes émettrices et réceptrices

Par conséquent, le système regroupant tous les

symboles reçus simultanément par les Nr antennes

pourrait être modélisé par la forme vectorielle suivante

:

y(k)=H(k).x(k)+b(k) (2.2)

où y(k)=[y1(k), y2(k), ...,

yNr(k)]T représente le vecteur des symboles

reçus de taille Nr x

1,

x(k)=[x1(k),x2(k),...,xNt(k)]T représente le vecteur

des symboles émis de taille Nt x

1,

b(k)=[b1(k),b2(k),...,bNr(k)]T représente le

vecteur de bruit BBAG perturbant les Nr antennes de taille

h k h k h k

11 1 1

( ) ( ) ( )

? ?

t Nt

? ? ? ? ?

|

Nr x 1 et H(k)=

|

hr

|

( ) ( ) ( )

k h k h k

? ?

rt rNt

1 ,1 ,

|

de taille NrxNt.

|

26

? ? ? ? ?

,1 ,

( ) ( ) ( )

k h k h k

hNr

? ?

Nr t NrNt

On rappelle que si la moyenne des évanouissements du

canal radio-mobile est nulle, alors l'enveloppe suit une loi de Rayleigh et le

canal est dit canal de Rayleigh [4]. C'est le modèle de canal que nous

allons considérer. Il y a deux types de canaux possibles, soit un canal

de Rayleigh classique ou ergodique, où les coefficients hrt

changent aléatoirement et indépendamment à chaque

période symbole, soit un canal quasi-statique ou Rayleigh par bloc, qui

garde constante les valeurs de hrt à l'intérieur d'un

même bloc. On considère par la suite un canal de Rayleigh par bloc

où le canal reste constant durant T utilisations du canal.

L'équation (2.2) devient alors :

y()=H.x()+b(), pour=1, ..., T. (2.3)

Pour les systèmes MIMO, il existe 2 techniques principales

utilisées dans les chaînes de transmission [4] :

27

- Le multiplexage spatial ;

- Le codage espace-temps.

Avant de présenter le multiplexage spatial qu'on

considèrera dans la suite de ce travail, on décrit

brièvement le principe du codage spatio-temporel.

3.1. Le codage espace-temps

Le principe du codage espace-temps ou space-time (ST) consiste

à recevoir des codes pour les systèmes MIMO en introduisant une

dépendance entre le domaine spatial et temporel afin d'exploiter la

diversité spatiale à l'émission et minimiser les effets

d'évanouissements dûs au canal radio-mobile. Le codage ST est

utilisé pour les systèmes MIMO sous deux grandes

catégories : les codes ST en treillis et les codes ST en bloc.

3.1.1. Les codes ST en treillis

Les codes ST en treillis ont été proposés

par Tarokh et al [15]. Dans cette catégorie, le principe du codage

consiste à combiner le codage canal avec la modulation sur les antennes

émettrices. En effet, le codage ST en treillis crée des relations

entres les symboles à la fois en espace et en temps. Le codeur ST en

treillis utilise un treillis à états où chaque état

Ek+1 dépend des bits d'information à coder et de

l'état Ek.

La réception est basée sur le décodage des

symboles reçus en utilisant un algorithme de recherche de chemin le plus

probable dans la ressemblance aux symboles émis.

Cette technique combine l'avantage de la diversité

spatiale avec le gain du codage. Néanmoins, elle présente un

inconvénient dans la complexité de l'algorithme de

décodage qui augmente rapidement avec le nombre d'antennes

d'émission.

3.1.2. Les codes ST en bloc

Plusieurs codes ST en bloc existent dans la littérature

[16] [15] [4]. Parmi ces codes on trouve les codes ST en bloc orthogonaux qui

sont définis comme une opération de modulation d'un bloc de

symboles à la fois dans l'espace et dans le temps, créant ainsi

des séquences orthogonales transmises par des antennes émettrices

différentes [15] [16]. Ces codes présentent l'avantage de la

faible complexité du décodeur.

Le schéma d'Alamouti pour deux antennes

d'émission comporte la structure de codage

représentée

dans la figure 2.6. Ce schéma de

décodage a été déjà intégré

dans la norme UMTS. D'après ce

schéma, on constate que l'envoi

de deux symboles nécessite deux antennes d'émission, deux

temps

de symboles et un codage spécial pour que les

séquences formées par les deux symboles soient orthogonales. Il

existe d'autres constructions de codes ST en blocs : les codes en couches, les

codes à dispersion linéaire, les codes algébriques, etc

[4].

Figure 2.6. Schéma d'Alamouti pour le cas des antennes

en émission

La technique de codage ST ne sera pas traitée dans ce

travail, mais le lecteur intéressé peut se référer

à [4].

3.2. Multiplexage spatial

Le multiplexage spatial consiste à démultiplexer

la séquence de données en Nt trains de données qui sont

ensuite transmis par les Nt antennes émettrices. C'est le schéma

qui a été proposé sous le nom de Bell Labs Layered

Space-Time (BLAST) par Foschini et al [14]. La théorie de l'information

a montré que la capacité d'un canal MIMO, c'est-à-dire le

débit maximal que l'on peut transmettre sans erreurs, peut être

atteinte avec le multiplexage spatial. Foschini et al on proposé deux

structures de BLAST : D-BLAST (Diagonal BLAST) et V-BLAST (Vertical BLAST)

[14]. On ne considère dans cette étude que l'architecture V-BLAST

pour son efficacité et pour sa simplicité et la faible

complexité de son décodage.

Le processus de démultiplexage de données utilisant

l'architecture V-BLAST pourrait être représenté par le

diagramme de la figure 2.7.

|

x x

1 1

Nt

|

?

|

|

(x1,x2,...,xk,...)

|

|

x x

2 2

Nt

|

?

|

28

? ? ?

Figure 2.7. Diagramme de la technique de démultiplexage

V-BLAST

Dans cette étude, on suppose une connaissance parfaite du

canal à la réception. En pratique, le canal est estimé par

le récepteur à chaque paquet transmis grâce à une

séquence d'apprentissage.

29

L'inconvénient du multiplexage spatial est qu'il ne

peut pas être utilisé lorsque le nombre d'antennes en

réception est inférieur au nombre d'antennes en émission

car le récepteur aura le problème d'un système

indéterminé d'équations linéaires.

3.3. Les techniques de détection pour le multiplexage

spatial

Dans ce sous-paragraphe, on va décrire des techniques de

détection pouvons être utilisées à la

réception pour retrouver les symboles émis sur les Nt antennes

d'émission.

Figure 2.8. Bloc d'égalisation pour le multiplexage

spatial

Après l'envoi des symboles sur les antennes

d'émission, les symboles sont altérés par le canal de

transmission et par le bruit BBAG. A la réception, on applique une

technique d'égalisation au vecteur reçu afin de

récupérer le vecteur de symboles émis en supposant que le

canal de transmission est constant pendant la transmission et parfaitement

estimé, et le rapport signal sur bruit (SNR) est aussi parfaitement

estimé (figure 2.8). On rappelle que le rapport signal sur bruit est

défini par le rapport

de la variance du signal x 2 sur la variance du bruit n 2 :

2 (2.4)

x

S N R 2

n

3.3.1. Techniques de détection linéaires

Les techniques de détection linéaire les moins

complexes sont basés sur l'un des critères suivants :

- le critère de forçage à zéro

(ZF);

- le critère de minimisation de l'erreur quadratique

moyenne (MMSE).

a) Récepteur ZF

Un égaliseur linéaire ZF minimise la forme

quadratique suivante :

y ~ Hx R y ~ Hx

† 1

J ZF à n à(2.5)

où Rn est la matrice de covariance du bruit

[17], y est le vecteur reçu par les Nr antennes

réceptrices correspondant au signal émis x (équation 2.3)

et H est la matrice de canal NrxNt.

En dérivant JZF par rapport à xà

et sachant que cette dérivée doit être nulle, on obtient

:

†

(2.6)

(2.7)

? ( à ) 2 1 ( à ) 0

y - Hx R y - Hx

?xà n

Ce qui donne alors :

.

† †

~1 ~1

~1

x = H R H H R y

à n n

Pour le cas d'un bruit BBAG, on a :

Rn= n 2 I, (2.8)

Et l'expression (2.7) devient :

|

x = H H H y

à ~1

† †

|

(2.9)

|

Ainsi la matrice d'égalisation est :

GZF = H H H .

† †

~1

(2.10)

b) Récepteur MMSE

Un récepteur MMSE est obtenu en minimisant l'erreur

quadratique moyenne [17] suivante :

|

†

J MMSE E x ~ x x ~ x

à à

|

(2.11)

|

D'après l'équation (2.3), on a y=Hx+b. On cherche

la matrice d'égalisation GMMSE qui vérifie :

xà =GMMSEy = GMMSEHx+GMMSEb. (2.12)

En développant JMMSE , on montre facilement que

:

†

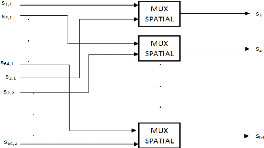

J MMSE E Trace à à