III.6.2.1.1. Convertisseur à approximations

successives :

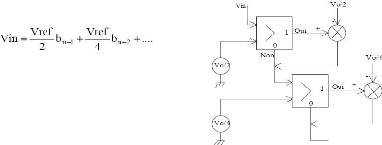

Principe : On

détermine les valeurs des différents bits l'un après

l'autre en commençant par le MSB, un peu à la manière

d'une marchande de marché :

Figure .III.3 : Principe de la pesée

successive

Le signal est comparé à une tension de

référence: Vo/2. S'il est supérieur, on lui retranche

cette valeur et on met le bit de comparaison à '1', sinon on met le bit

de comparaison à '0' et on le compare à la tension suivante.

On effectue ainsi un encadrement progressif de plus en plus fin.

Ainsi pour un CAN N bits, en N coups on obtient la conversion.

Il est plus lent que le Flash. Ainsi pour 16 bits, il lui faut

en moyenne un temps de conversion de 10jts. Il est très adapté

à des signaux audio.

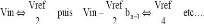

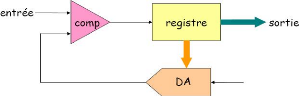

III.6.2.1.2. Simple rampe / tracking :

Principe : A la valeur de la

tension d'entrée on fait correspondre une impulsion dont la largeur est

proportionnelle à cette tension. Cette impulsion vient contrôler

l'autorisation à s'incrémenter d'un compteur. On

génère ainsi le code binaire de sortie en comptant plus ou moins

longtemps en fonction de l'amplitude du signal à convertir.

Figure .III.4 : Principe du convertisseur simple

rampe

Caractéristiques :

> Les Avantages :

· Simple et peu coûteux.

· Inconvénients :

· N dépend de C donc de la tolérance sur

C.

· Lent car nécessite 2N cycles d'horloges

pour effectuer une conversion.

· Comme il n'y a pas de synchronisme entre l'horloge et le

RAZ, cela induit une imprécision

de 1 période au début

et à la fin de la conversion soit une erreur moyenne de 1,5 quantum.

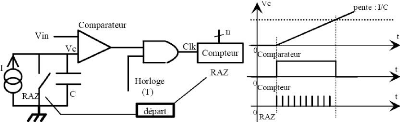

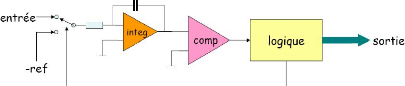

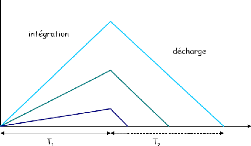

III.6.2.1.3. Double rampe (intégrateur) :

Principe : On effectue une

double intégration de manière à faire s'annuler les

erreurs dues aux composants :

Figure .III.5 : Architecture du convertisseur

double rampe

- phase 1 : intégration de l'entrée pendant un

temps T1

- phase 2 : décharge de l'intégrateur vers 0

à vitesse constante.

- Le temps T2 mis à décharger l'intégrateur

donne la valeur d'entrée

Chapitre III conception matériel

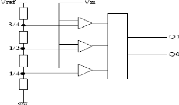

III.6.2.1.4. Parallèle (flash) : Principe :

Figure .III.6 : le convertisseur

Flash

C'est un réseau de comparateur mis en parallèle.

Un codage sur n bits nécessite 2n-1 comparateurs et

résistances.

Facteurs clefs : temps de

conversion, résolution, précision, linéarité, codes

manquants, fenêtre d'acquisition, impédance d'entrée,

bruit

III.6.3. Effecteurs : influent sur l'environnement :

moteurs, servomoteurs, valves, restitution de son

(haut-parleurs, buzzers, ...), relais, afficheurs, Contrôleurs

d'effecteurs, conversion N/A, amplification, interrupteurs de puissance (IGBT,

MOS,...),relais, générateurs PWM ,FPAA

III.6.3.1. Les Convertisseurs Numériques

Analogiques :

Définition : On souhaite

à partir d'une information numérique, codée sur n bits,

récupérer un signal analogique, image du numérique.

Principe : Chaque bit va

être associé à un interrupteur qui connectera (1) ou non

(0) une source (de courant) sur la sortie.

- sortie quantifiée et échantillonnée -

filtrage souvent nécessaire !

Facteurs clefs :

résolution, linéarité, temps de conversion, glitches :

échantillonneur, bloqueur en sortie, bruit...

|