II.6.2.8.1. La génération d'enveloppes de

simulation :

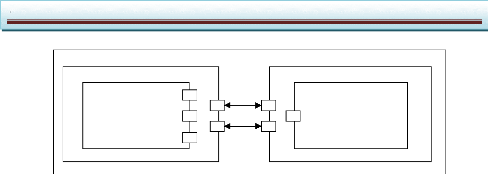

Le flot permet d'effectuer des simulations du système

à tout niveau d'abstraction, et même en mélangeant les

niveaux d'abstraction. La technique de base consiste à encapsuler les

divers composants à simuler dans des enveloppes qui adaptent le niveau

de leurs communications à celui de la simulation globale. La figure

II.12 illustre l'utilisation de ces enveloppes : à l'intérieur de

chacune se trouve un composant qui est simulé à un niveau

d'abstraction qui peut être inférieur (module A) égal ou

supérieur (module B) au niveau d'abstraction de la simulation. Ces

enveloppes permettent aussi d'adapter les divers simulateurs entre eux, comme

par exemple un simulateur VHDL (module B) et un simulateur systemC.

Chapitre II conception des logiciels embarqués

Simulation SystemC

Enveloppe A

Module A

VHDL

Niveau : micro-architecture

Enveloppe B

Module B systemC Niveau : fonctionnel

Figure II.12. Enveloppes de

simulation

Un outil qui permet de générer ces enveloppes

est basé sur le même principe que la génération

d'interface : la bibliothèque contient les trois types de composants

précédemment cités, mais le bus interne devient une API

(application programming interface) de simulation.

II.6.2.8.2. La cosimulation :

Grâce aux enveloppes, il est possible d'effectuer des

validations par cosimulation pour toutes les étapes du flot, ou

même sur des composants situés à des étapes

différentes. Plus le niveau d'abstraction est élevé, plus

la simulation est rapide, et plus le niveau est bas, plus la simulation est

précise. Cette cosimulation est multiniveau, mais elle peut être

aussi multilangage. La raison de telles cosimulations est que très

souvent un langage est adapté pour la simulation de certaines parties

d'un système, mais inadapté pour d'autres. Par exemple les

simulateurs VHDL sont bons pour les circuits mais pas pour la mécanique

qui est mieux modélisée par Matlab.

Pour effectuer une cosimulation, chaque simulateur est

exécuté dans un processus différent. Un processus de

contrôle gère l'ensemble des communications et synchronisations

entre les simulateurs par le biais de mémoires partagées. Le

modèle temporel utilisé est le modèle synchrone : chaque

simulateur exécute un pas de calcul, puis toutes les données sont

échangées grâce au processus de routage. Une fois que les

communications sont achevées, un autre pas de calcul peut être

effectué.

Le processus de contrôle est décrit en systemC.

Cela permet de l'utiliser pour décrire des parties matérielles ou

logicielles au niveau macroarchitecture, sans avoir à utiliser un

simulateur externe. Il est généré en même temps que

les enveloppes à partir de la bibliothèque de simulation.

II.6.2.9. Utilisation des résultats de

simulation :

Les simulations pourront servir de base pour mettre en place

une méthodologie d'évaluation qui permettra dans un premier temps

de guider les choix du concepteur dans l'étape de synthèse, puis

d'automatiser cette synthèse avec recherche d'optimum. Pour ce faire, il

faudra définir des modèles de performance et des heuristiques

permettant de les composer en même temps que l'on compose les divers

modules des systèmes à générer.

|