INTRODUCTION

Un réseau informatique est un ensemble

d'équipements interconnectés qui servent à acheminer un

flux d'informations. Sa naissance est le fruit du mariage entre Informatique et

Télécommunications.

Afin de pouvoir bien acheminer l'information, le réseau

informatique utilise ce qu'on appelle le processus de routage. Le routage

cherche le chemin le plus efficace entre les différents noeuds du

réseau d'une unité à une autre. Le matériel au

centre de ce processus est le routeur.

Un routeur est une unité de couche réseau qui

utilise des protocoles de routage pour déterminer le chemin optimal

par lequel acheminer le trafic réseau. Les protocoles de routage prenant

en charge le protocole routé IP sont par exemple les protocoles RIP,

IGRP, OSPF, BGP et EIGRP.

Les protocoles OSPF utilisent comme algorithme de routage,

l'algorithme de dijkstra pour déterminer le chemin optimal à

assigner au flux de l'information. Cependant l'information n'étant plus

seulement transmise comme donnée, plusieurs autres facteurs entrent

maintenant en jeu parmi lesquels on peut citer celui de la qualité de

service. Les processeurs ordinaires sur lesquels tournent ces algorithmes de

routage éprouvent de plus en plus des difficultés croissantes

avec les qualités et les exigences de plus en plus grandes des services

devant être rendu par les réseaux. En effet, l'augmentation en

complexité du calcul est exponentiellement transformée en une

augmentation en qualité de service, et pour que le réseau puisse

atteindre des performances acceptables, il y a nécessité d'une

augmentation en ressource opératoire.

A ce stade donc, le réseau doit pourvoir combiner

flexibilité et vitesse, aucun compromis ici n'est

toléré ; d'où la nécessité de se

tourner vers de nouvelles technologies plus performantes que celles

rencontrées sur les processeurs actuels, des technologies permettant de

combiner à la fois la reconfigurabilité et la rapidité

des calculs, en d'autres termes d'allier à la flexibilité du

software, la vitesse du hardware. La technologie FPGA est une technologie

pareille.

Il est vrai que le premier réflexe face à ce

problème de flexibilité et de rapidité, la solution

première ne fut pas tout d'abord de se tourner vers les circuits

reprogrammables mais plutôt vers la conception de nouveaux protocoles de

routage encore plus complexe que les précédents. Mais

heureusement les concepteurs de protocoles se rendirent vite compte que le

problème n'était autre que le processeur qui effectue les

calculs. Plusieurs versions d'implémentation d'algorithmes sur FPGA

virent donc le jour.

L'objectif de notre travail est donc de présenter la

méthodologie d'implantation d'un de ces algorithmes de routage qui est

ici celui de DIJKSTRA sur un circuit FPGA. Le plan de notre travail est donc

réparti de la manière suivante : au premier chapitre nous

allons présenter très clairement ce que c'est que le routage

dans les réseaux informatiques.

Dans ce chapitre nous allons tout particulièrement

insister sur le protocole de routage OSPF. Ensuite dans le chapitre deux, nous

présenterons très clairement les circuits reprogrammables en

détaillant les processeurs FPGA et en insistant sur leur structure, leur

fonctionnement et leur programmation. Dans le chapitre trois, nous allons

présenter de façon brève mais concise, le langage VHDL et

la conception de circuits. Dans le chapitre quatre, nous allons

présenter la méthodologie d'implémentation

c'est-à-dire comment à l'aide du langage VHDL nous avons

implémenté l'algorithme de DIJKSTRA dans un circuit FPGA. Dans le

chapitre cinq, après simulation, nous présenterons les

résultats et nous effectuerons une comparaison avec les résultats

obtenus par les processeurs ordinaires. Nous clôturerons ce travail par

une conclusion générale.

CHAPITRE 1 :

LE ROUTAGE DANS LES RESEAUX INFORMATIQUES

1.1 Introduction

Le routage est une fonction de la couche 3 (couche réseau)

du modèle OSI (Open System Internet). C'est un système

d'organisation hiérarchique (voir figure1.1) qui permet de regrouper des

adresses individuelles. Ces dernières sont traitées comme un tout

jusqu'à ce que l'adresse de destination soit requise pour la livraison

finale des données.

LIAISON DE DONNEES

RESEAU

TRANSPORT

SESSION

PRESENTATION

APPLICATION

PHYSIQUE

APPLICATION

PRESENTATION

SESSION

TRANSPORT

RESEAU

LIAISON DE DONNEES

PHYSIQUE

7

6

5

4

ROUTAGE

3

2

1

UFigure1.1 :Ucouche

réseauU

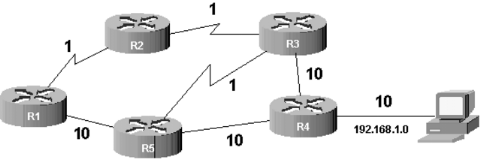

Le routage cherche le chemin le plus efficace d'une

unité à une autre (voir figure 1.2). Le matériel au centre

du processus de routage est le routeur (figure1.3).

A

F

![]() Figure1.2 : lLle

routage Figure1.2 : lLle

routage

Figure1.3 : Routeur Figure1.3 : Routeur

Il possède les deux fonctions principales suivantes:

· Le routeur gère les tables de routage et

s'assure que les autres routeurs ont connaissance des modifications

apportées à la topologie du réseau. Il se sert des

protocoles de routage pour échanger les informations de réseau.

· Le routeur détermine la destination des paquets

à l'aide de la table de routage lorsque ceux-ci arrivent à l'une

de ses interfaces. Il les transfère vers la bonne interface, ajoute les

informations de trame de cette interface, puis transmet la trame vers

l'extérieur.

Un routeur est une unité de couche réseau qui

utilise une ou plusieurs métriques pour déterminer le chemin

optimal par lequel acheminer le trafic réseau. Les métriques de

routage sont les valeurs qui permettent de définir le meilleur

chemin.

Les routeurs permettent d'interconnecter les segments d'un

réseau ou des réseaux entiers. Leur rôle consiste à

acheminer les trames de données entre les réseaux, en fonction

des informations de la couche 3. Ils prennent des décisions logiques

quant au meilleur acheminement possible des données, puis redirigent les

paquets vers le port de sortie approprié afin qu'ils soient

encapsulés pour la transmission. Les phases d'encapsulation et de

désencapsulation se produisent à chaque passage d'un paquet dans

un routeur. Le routeur doit en effet dés encapsuler la trame de

données de la couche 2 pour accéder à l'adresse de couche

3 et l'examiner. L'encapsulation consiste à fractionner le flux de

données en segments et à ajouter les en-têtes et les en

queues appropriés avant de transmettre les données. Le processus

de dés encapsulation, quant à lui, consiste à retirer les

en-têtes et les en-queues, puis à recombiner les données en

un flux continu (voir figure1.4 et figure1.5).

Réseau

Liaison de données

Physique

Réseau

En-tête

Données

Trame

En-tête

Réseau

En-tête

Données

Trame

En-queu

![]() Figure1.4 :

UencapsulationU Figure1.4 :

UencapsulationU

Réseau

Liaison de données

Physique

Réseau

En-tête

Données

Trame

En-tête

Réseau

En-tête

Données

Trame

En-queu

![]() UFigure1.5U :

UdésencapsulationU UFigure1.5U :

UdésencapsulationU

1.2 UProtocole routé et protocole de routage

[1]

Les protocoles routés ou routables sont utilisés

au niveau de la couche réseau afin de transférer les

données d'un hôte à l'autre via un routeur. Les protocoles

routés transportent les données sur un réseau. Les

protocoles de routage permettent aux routeurs de choisir le meilleur chemin

possible pour acheminer les données de la source vers leur

destination.

Le protocole routé englobe notamment les fonctions

suivantes:

· Il inclut n'importe quelle suite de protocoles

réseau capable de fournir assez d'informations dans l'adresse de couche

réseau pour permettre au routeur d'effectuer le transfert vers

l'unité suivante, jusqu'à la destination finale.

· Il définit le format et l'usage des champs dans

un paquet.

Le protocole IP (Internet Protocol) et le protocole IPX

(Internetwork Packet Exchange) de Novell, mais aussi DECnet, AppleTalk, Banyan

VINES et Xerox Network Systems (XNS), sont des exemples de protocoles

routés.

Les routeurs utilisent des protocoles de routage pour

échanger des tables de routage et partager d'autres informations

d'acheminement. En d'autres termes, les protocoles de routage permettent aux

routeurs d'acheminer les protocoles routés.

Les fonctions du protocole de routage sont en partie les

suivantes:

· Il fournit les processus utilisés pour partager

les informations d'acheminement.

· Il permet aux routeurs de communiquer entre eux afin de

mettre à jour et de gérer les tables de routage.

Les protocoles de routage prenant en charge le protocole

routé IP sont par exemple les protocoles RIP, IGRP, OSPF, BGP et EIGRP.

1.3 ULa détermination du chemin [1]

La détermination du chemin se produit au niveau de la

couche réseau. Ce processus permet au routeur de comparer l'adresse de

destination aux routes disponibles dans sa table de routage et de choisir le

meilleur chemin possible. Les routeurs acquièrent ces chemins soit par

l'intermédiaire du routage statique, soit par l'intermédiaire du

routage dynamique. Les chemins configurés manuellement par

l'administrateur réseau sont appelés «routes

statiques». Ceux que le routeur a acquis d'autres routeurs à l'aide

d'un protocole de routage sont dits «routes dynamiques».

La détermination du chemin permet au routeur de choisir

le port à partir duquel envoyer un paquet pour que celui-ci arrive

à destination. On appelle ce processus le routage d'un paquet. Chaque

routeur rencontré sur le chemin du paquet est appelé un saut. Le

nombre de sauts constitue la distance parcourue. La détermination du

chemin peut être comparée à la situation où une

personne conduit sa voiture d'un endroit de la ville à un autre. Le

conducteur consulte une carte qui lui indique les rues par lesquelles passer

pour arriver à sa destination, tout comme le routeur consulte sa table

de routage. Il passe d'un carrefour à un autre, de la même

façon qu'un paquet circule d'un routeur à un autre lors de chaque

saut. À chaque carrefour, le conducteur peut choisir de prendre à

gauche, à droite ou de continuer tout droit. Il en va de même pour

le routeur lorsqu'il choisit le port de sortie à partir duquel le paquet

sera envoyé.

Le conducteur prend ses décisions en fonction de

certains facteurs, comme l'état du trafic, la limitation de vitesse, le

nombre de voies, les péages et si une route est fréquemment

fermée ou pas. Il est parfois plus rapide de prendre le chemin le plus

long en passant par des petites routes peu fréquentées que de

prendre l'autoroute embouteillée. De même, les routeurs vont

prendre leurs décisions en fonction de la charge, de la bande passante,

du délai, du coût et de la fiabilité d'une liaison de

réseau.

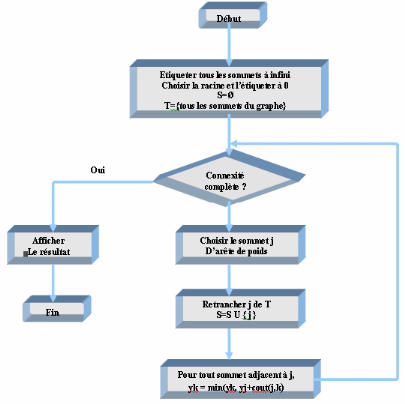

Les processus impliqués dans la sélection du

chemin pour chaque paquet sont illustrés dans la figure 1.6 :

Transmission du paquet de données à l'interface de

l'entrée de la table de routage

Application du masque de l'entrée de la table de routage

sur l'adresse IP de destination

Retrait de l'en tête de trame du paquet

Réception du paquet sur l'interface

Encapsulation du paquet de données dans la trame

appropriée

Comparaison de l'adresse de destination masquée avec

l'adresse réseau de l'entrée

Extraction de l'adresse IP de destination du paquet

Les données sont elles

destinées

au routeur ?

Oui

Transmission de la nouvelle trame

Existe il une

Correspon-

dance ?

Utilisation de la première entrée de la table

routage

Non

Oui

Rejet des données

Fin

Fin

Non

Existe il une route par défaut ?

Existe il une autre entrée de la table de

routage ?

Non

Fin

Oui

Non

Rejet des données

Accès à l'entrée suivante

UFigure1.6 :

UProcessus de routage [1]

U

1.4 UTables de routage

Les routeurs emploient des protocoles de routage pour

construire et gérer les tables de routage contenant les informations

d'acheminement. Le processus de sélection du chemin en est ainsi

facilité. Les protocoles de routage placent diverses informations

d'acheminement dans les tables de routage. Le contenu de ces informations varie

selon le protocole de routage utilisé. Les tables de routage contiennent

les informations nécessaires à la transmission des paquets de

données sur les réseaux connectés. Les équipements

de couche 3 interconnectent les domaines de broadcast ou les réseaux

LAN. Le transfert des données nécessite un système

d'adressage hiérarchique.

Les routeurs conservent les informations suivantes dans leurs

tables de routage:

· Type de protocole: cette information identifie le type

de protocole de routage qui a créé chaque entrée.

· Associations du saut suivant: indique au routeur que la

destination lui est directement connectée, ou qu'elle peut être

atteinte par le biais d'un autre routeur appelé le «saut

suivant» vers la destination finale. Dès réception d'un

paquet, le routeur vérifie l'adresse de destination et tente de trouver

une correspondance dans sa table de routage.

· Métrique de routage: les métriques

utilisées varient selon les protocoles de routage et permettent de

déterminer les avantages d'une route sur une autre. Par exemple, le

protocole RIP se sert d'une seule métrique de routage : le nombre de

sauts. Le protocole IGRP crée une valeur de métrique composite

à partir des métriques de fiabilité, de délai, de

charge et de bande passante.

· Interfaces de sortie: cette information désigne

l'interface à partir de laquelle les données doivent être

envoyées pour atteindre leur destination finale.

Les routeurs s'envoient des messages afin de mettre à

jour leurs tables de routage. Certains protocoles de routage transmettent ces

messages de manière périodique. D'autres ne les envoient que

lorsque des changements sont intervenus dans la topologie du réseau.

Certains transmettent l'intégralité de la table dans leurs

messages de mise à jour alors que d'autres se contentent d'envoyer les

modifications. L'analyse des mises à jour de routage provenant de

routeurs directement connectés permet aux routeurs de créer et de

gérer leur table de routage.

Exemple d'une table de routage sous Windows

XP :

Itinéraires actifs :

Destination réseau Masque réseau Adr.

Passerelle Adr. Interface Métrique

0.0.0.0 0.0.0.0

192.168.0.1 192.168.0.23 20

127.0.0.0 255.0.0.0 127.0.0.1

127.0.0.1 1

192.168.0.0 255.255.254.0 192.168.1.23

192.168.1.23 20

192.168.1.23 255.255.255.255 127.0.0.1

127.0.0.1 20

192.168.1.255 255.255.255.255 192.168.1.23

192.168.1.23 20

224.0.0.0 240.0.0.0 192.168.1.23

192.168.1.23 20

255.255.255.255 255.255.255.255 192.168.1.23

192.168.1.23 1

Passerelle par défaut : 192.168.0.1

UTableau1.1U :

UTable de routage [2]

U Explication de la tableU

1. Destination 0.0.0.0

C'est la route que les paquets vont prendre lorsqu'ils n'on

pas trouvé un meilleur chemin. En fait, c'est la route

par défaut, reprise à la ligne 8.

C'est la ligne la plus intéressante, parce qu'elle fait

intervenir une adresse de passerelle et une adresse d'interface (192.168.0.23)

différentes.

Cette ligne veut dire en français, "Lorsqu'on ne sait

pas par où il faut passer, on va emprunter l'interface 192.168.0.23 pour

joindre la passerelle 192.168.0.1. C'est elle qui décidera pour la suite

du chemin".

2. Destination 127.0.0.0

C'est la boucle interne, celle qui permet à

l'hôte de se parler à lui même.

3. Destination 192.168.0.0

C'est mon réseau local. Cette ligne indique que la

passerelle est 192.168.1.23, de même que l'adresse de l'interface.

4. Pour atteindre 192.168.1.23, c'est à dire

moi-même, il faudra utiliser 127.0.0.1 (adresse interne toujours la

même sur tous les hôtes quelque soit l'OS).

5. Pour réaliser un broadcast sur mon réseau, il

faudra utiliser 192.168.1.23

6. Si l'on souhaite faire du multicast, même chose

7. Si l'on souhaite faire du broadcast étendu, encore

la même chose.

8. La passerelle par défaut est indiquée de

façon explicite.

1.5 UAlgorithmes et métriques de routage [1]

Un algorithme est une solution détaillée d'un

problème. Les algorithmes utilisés pour définir le port

auquel envoyer un paquet diffèrent selon les protocoles de routage. Ils

reposent sur l'utilisation de métriques pour prendre ce type de

décision.

Les protocoles de routage sont conçus pour

répondre à un ou plusieurs des objectifs suivants :

· Optimisation : capacité d'un algorithme de

routage à sélectionner le meilleur chemin. Ce dernier sera choisi

en fonction des métriques et de la pondération utilisées

dans le calcul. Par exemple, un algorithme peut utiliser à la fois le

nombre de sauts et le délai comme métriques, mais

considérer que le délai doit prévaloir dans le calcul.

· Simplicité et réduction du temps

système : plus l'algorithme est simple et plus il sera traité

efficacement par le processeur et la mémoire du routeur. Ce

paramètre est important si le réseau veut pouvoir évoluer

vers des proportions plus conséquentes, comme Internet.

· Efficacité et stabilité : un algorithme

de routage doit pouvoir fonctionner correctement dans des circonstances

inhabituelles ou imprévues, comme les défaillances de

matériels, les surcharges et les erreurs de mise en oeuvre.

· Flexibilité : un algorithme de routage doit

pouvoir s'adapter rapidement à toutes sortes de modifications du

réseau, touchant par exemple la disponibilité et la

mémoire du routeur, la bande passante ou le délai réseau.

· Rapidité de convergence : la convergence est le

processus par lequel tous les routeurs s'entendent sur les routes disponibles.

Lorsqu'un événement sur le réseau entraîne des

modifications au niveau de la disponibilité d'un routeur, des mises

à jour sont nécessaires afin de rétablir la

connectivité du réseau. Une convergence lente des algorithmes de

routage peut empêcher la livraison des données.

Les algorithmes de routage utilisent différentes

métriques pour déterminer la meilleure route (voire

tableau1.5a).

|

Protocole

|

Métrique

|

Nombre maxi de routeur

|

Origine

|

|

Protocole RIP

|

Nombre de sauts

|

15

|

Xerox

|

|

Protocole IGRP

|

· Bande passante

· Charge

· Délai

· Fiabilité

|

255

|

Cisco

|

UTableau1.2U :

UAlgorithmes et métriques de

routageU

Chacun d'eux interprète à sa façon ce qui

est le mieux. L'algorithme génère un nombre, appelé valeur

métrique, pour chaque chemin traversant le réseau. Les

algorithmes de routage perfectionnés effectuent la sélection du

chemin en fonction de plusieurs métriques combinées en une valeur

composite. Généralement, les valeurs métriques faibles

indiquent le meilleur chemin.

Les métriques peuvent être calculées sur

la base d'une seule caractéristique de chemin, comme elles peuvent

l'être sur la base de plusieurs. Les métriques les plus

communément utilisées par les protocoles de routage sont les

suivantes:

· Bande passante : la bande passante représente la

capacité de débit d'une liaison. Une liaison Ethernet de 10

Mbits/s est généralement préférable à une

ligne louée de 64 Kbits/s.

· Délai : le délai est le temps

nécessaire à l'acheminement d'un paquet, pour chaque liaison, de

la source à la destination. Il dépend de la bande passante des

liaisons intermédiaires, de la quantité de données pouvant

être temporairement stockées sur chaque routeur, de la congestion

du réseau et de la distance physique.

· Charge : la charge est la quantité de trafic sur

une ressource réseau telle qu'un routeur ou une liaison.

· Fiabilité : la fiabilité se rapporte

habituellement au taux d'erreurs de chaque liaison du réseau.

· Nombre de sauts : le nombre de sauts est le nombre de

routeurs par lesquels un paquet doit passer avant d'arriver à

destination. Chaque routeur équivaut à un saut. Un nombre de

sauts égal à 4 signifie que les données doivent passer par

quatre routeurs pour atteindre leur destination. Lorsque plusieurs chemins sont

possibles, c'est le chemin comportant le moins de sauts qui est

privilégié.

· Tops : délai d'une liaison de données

utilisant les tops d'horloge d'un PC IBM, un top d'horloge correspondant

environ à 1/18 seconde.

· Coût : le coût est une valeur arbitraire,

généralement basée sur la bande passante, une

dépense monétaire ou une autre mesure, attribuée par un

administrateur réseau.

1.6 UExemple de protocole de routageU : OSPF (Open

Shortest Path First) [3] [4]

Le protocole OSPF est un protocole de routage à

état de liens mis au point par l'IETF (Internet Engineering Task Force)

en 1988.

Nous allons le détailler dans cette partie parce qu'il

est basé sur l'algorithme de DIJKSTRA pour la détermination du

plus court chemin.

En fait le problème soumis à notre étude

est le suivant :

Nous sommes à l'entrée d'un réseau WAN

(Wide Area Network), nous recevons continuellement un flux de données

à notre entrée et nous devons acheminer ces données sur

le chemin (prochain routeur) le moins coûteux au travers de l'utilisation

d'un protocole approprier. Le protocole le plus efficace à

présent est le MPLS (Multi-Protocol Label Switching) [5]. Ce dernier

utilise pour le calcul du chemin répondant aux contraintes

spécifiées les extensions du protocole OSPF. C'est la raison pour

laquelle nous nous intéressons à OSPF.

Sans donc entrer trop dans les détails, nous allons

présenter ici de façon succincte le protocole OSPF.

1.6.1 UFonctionnement d'OSPF

À l'intérieur d'une même zone, les

routeurs fonctionnant sous OSPF doivent préalablement remplir les

tâches suivantes avant de pouvoir effectuer leur travail de routage :

1. Section 1.6.3, « Établir la liste des routeurs

voisins : Hello, my name is R1 and I'm an OSPF router. »,

2. Section 1.6.4, « Élire le routeur

désigné et le routeur désigné de secours »,

3. Section 1.6.5, « Découvrir les routes

»,

4. Section 1.6.6, « Élire les routes à

utiliser »,

5. Section 1.6.7, « Maintenir la base topologique

».

1.6.2 UETAT INITIALU

Le processus de routage OSPF est inactif sur tous les routeurs

de la Figure1.6.2a, « Exemple de topologie ».

UFigure1.7 : UExemple

de topologie

1.6.3 UÉtablir la liste des routeurs voisins :

Hello, my name is R1 and I'm an OSPF router

Les routeurs OSPF sont bien élevés. Dès

qu'ils sont activés, ils n'ont qu'une hâte : se présenter

et faire connaissance avec leurs voisins. En effet, lorsque le processus de

routage est lancé sur R1 (commande router Ospf), des paquets de

données (appelés paquets HELLO) sont envoyés sur chaque

interface où le routage dynamique a été activé

(commande network).

L'adresse multicast 224.0.0.5 est utilisée, tout

routeur OSPF se considère comme destinataire. Ces paquets ont pour but

de s'annoncer auprès de ses voisins. Deux routeurs sont dits voisins

s'ils ont au moins un lien en commun. Par exemple, sur la Figure1.6.2a, «

Exemple de topologie », R1 et R2 sont voisins mais pas R1 et R3.

Lorsque le processus de routage OSPF est lancé sur R2,

celui-ci récupère les paquets HELLO émis par R1 toutes les

10 secondes (valeur par défaut du temporisateur appelé hello

interval). R2 intègre l'adresse IP de R1 dans une base de données

appelée «base d'adjacences» (adjacencies database). Cette base

contient les adresses des routeurs voisins. On peut visionner son contenu

grâce à la commande show ip Ospf neighbor. R2 répond

à R1 par un paquet IP unicast. R1 intègre l'adresse IP de R2 dans

sa propre base d'adjacences. Ensuite, on généralise ce processus

à l'ensemble des routeurs de la zone.

Cette phase de découverte des voisins est fondamentale

puisque OSPF est un protocole à état de liens. Il lui faut

connaître ses voisins pour déterminer s'ils sont toujours

joignables et donc déterminer l'état du lien qui les relie.

1.6.4 U Élire le routeur désigné et

le routeur désigné de secours

Dans une zone OSPF composée de réseaux de

diffusion (broadcast networks) ou de réseau à accès

multiples sans diffusion (non broadcast multiple access networks ou NBMA), l'un

des routeurs doit être élu «routeur

désigné» (DR pour Designated Router) et un autre

«routeur désigné de secours» (BDR pour Backup

Designated Router). Le «routeur désigné» (DR) est un

routeur particulier qui sert de référent pour la base de

données topologique représentant le réseau.

Pourquoi élire un routeur désigné ? Cela

répond à trois objectifs :

· réduire le trafic lié à

l'échange d'informations sur l'état des liens (car il n'y a pas

d'échange entre tous les routeurs mais entre chaque routeur et le

DR),

· améliorer l'intégrité de la base

de données topologique (car cette base de données doit être

unique),

· accélérer la convergence.

Comment élire le DR ? Le routeur élu est celui

qui a la plus grande priorité (Router ID ou RID). La priorité est

un nombre sur 8 bits fixé par défaut à 1 sur tous les

routeurs. Pour départager les routeurs ayant la même

priorité, celui qui est élu a la plus grande adresse IP sur une

interface de boucle locale (loopback interface) ou sur un autre type

d'interface active. Le BDR sera le routeur avec la deuxième plus grande

priorité.

Afin de s'assurer que votre routeur

préféré sera élu DR, il suffit de lui affecter une

priorité supérieure à 1 avec la commande Ospf priority.

Vous devrez faire ceci avant d'activer le processus de routage sur les routeurs

car, une fois élu, le DR n'est jamais remis en cause même si un

routeur avec une priorité plus grande apparaît dans la zone.

1.6.5 UDécouvrir les routes

Il faut maintenant constituer la base de données

topologique. Les routeurs communiquent automatiquement les routes pour les

réseaux qui participent au routage dynamique (ceux

déclarés avec la commande network). Zebra et son successeur

Quagga étant multiprotocoles, ils peuvent également diffuser des

routes provenant d'autres sources que OSPF, grâce à la commande

redistribute.

Chaque routeur (non DR ou BDR) établit une relation

maître/esclave avec le DR. Le DR initie l'échange en transmettant

au routeur un résumé de sa base de données topologique via

des paquets de données appelés LSA (Link State Advertisement).

Ces paquets comprennent essentiellement l'adresse du routeur,

le coût du lien et un numéro de séquence. Ce numéro

est un moyen pour déterminer l'ancienneté des informations

reçues. Si les LSA reçus sont plus récents que ceux dans

sa base topologique, le routeur demande une information plus complète

par un paquet LSR (Link State Request). Le DR répond par des paquets LSU

(Link State Update) contenant l'intégralité de l'information

demandée. Ensuite, le routeur (non DR ou BDR) transmet les routes

meilleures ou inconnues du DR.

L'administrateur peut consulter la base de données

topologique grâce à la commande show ip Ospf database.

1.6.6 Élire les routes à

utiliser

Lorsque le routeur est en possession de la base de

données topologique, il est en mesure de créer la table de

routage. L'algorithme du SPF est appliqué sur la base topologique. Il en

ressort une table de routage contenant les routes les moins coûteuses.

Il faut noter que sur une base de données topologique

importante, le calcul consomme pas mal de ressources CPU car l'algorithme est

relativement complexe.

1.6.7 Maintenir la base topologique

Lorsqu'un routeur détecte un changement de

l'état d'un lien (cette détection se fait grâce aux paquets

HELLO adressés périodiquement par le routeur à ses

voisins), celui-ci émet un paquet LSU sur l'adresse multicast 224.0.0.6

: le DR et le BDR de la zone se considèrent comme destinataires.

Le DR et le BDR intègrent cette information à

leur base topologique. Le DR diffuse l'information sur l'adresse 224.0.0.5

(tous les routeurs OSPF sans distinction). C'est le protocole d'inondation.

Toute modification de la topologie déclenche une nouvelle

exécution de l'algorithme du SPF et une nouvelle table de routage est

constituée.

1.7 Conclusion du chapitre

Le problème soumis à notre étude se

trouve donc au niveau de cet algorithme SPF (shortest path first), en effet

nous devons ici accélérer son exécution en

l'implémentant sur des processeurs FPGA.

Il y a lieu de préciser ici que ce chapitre ne fut

conçue qu'à fin de donner un aperçu du routage, mais il ne

s'agit en aucun cas d'un cours sur le routage ou sur les protocoles de

routage, le routage étant en effet un domaine très vaste de

l'informatique.

Faisons remarquer cependant que malgré le faite que

notre travail soit centré sur les circuits reprogrammables, nous en

avons expressément fais abstraction ici car dans le prochain chapitre

nous nous y consacrerons.

CHAPITRE 2 : LES COMPOSANTS FPGA (FIELD

PROGRAMABLE GATE ARRAY)

2.1 Introduction U

Les progrès technologiques continus dans le domaine des

circuits intégrés ont permis la réduction des coûts,

de la consommation, et c'est maintenant un lieu commun d'affirmer que les

circuits intégrés spécifiques d'une application ont permis

une réduction de la taille des systèmes numériques ainsi

que la réalisation de circuits de plus en plus complexes, tout en

améliorant leurs performances et leur fiabilité. Aujourd'hui les

techniques de traitement numérique occupent une place majeure dans tous

les systèmes électroniques modernes grand public, professionnel

ou de défense. De plus, les techniques de réalisation de circuits

spécifiques, tant dans les aspects matériels (composants

reprogrammables, circuits pré caractérisés et

bibliothèques de macro fonctions) que dans les aspects logiciels

(placement routage, synthèse logique) font désormais de la

microélectronique une des bases indispensables pour la

réalisation de systèmes numériques performants. Elle

impose néanmoins une méthodologie de développement en CAO

très structurée.

Nous allons examiner les diverses technologies utilisables

pour la conception de circuits logiques avec leurs avantages et leurs

inconvénients afin d'expliciter l'intérêt de la technologie

FPGA.

2.2 ULes ASICS (Application Specific Integrated

Circuit)U

Dans un premier temps, nous allons rappeler quelques concepts

autour des circuits intégrés pour applications spécifiques

ASIC. Les circuits ASIC constituent la troisième

génération de circuits intégrés qui a vu le jour au

début des années 80. En comparaison des circuits

intégrés standards et figés proposés par les

fabricants, l'ASIC présente une personnalisation de son fonctionnement,

selon l'utilisation, accompagnée d'une réduction du temps de

développement, d'une augmentation de la densité

d'intégration et de la vitesse de fonctionnement. En outre sa

personnalisation lui confère un autre avantage industriel, c'est

évidemment la confidentialité. Ce concept d'abord

développé autour du silicium s'est ensuite étendu à

d'autres matériaux pour les applications micro-ondes ou très

rapides (GaAs par exemple).

Par définition, les circuits ASIC regroupent tous les

circuits dont la fonction peut être personnalisée d'une

manière ou d'une autre en vue d'une application spécifique, par

opposition aux circuits standards dont la fonction est définie et

parfaitement décrite dans le catalogue de composants. Les ASIC peuvent

être classés en plusieurs catégories selon leur niveau

d'intégration, en fait un ASIC est défini par sa structure de

base (réseau programmable, cellule de base, matrice, etc.). Sous le

terme ASIC deux familles sont regroupées, les semi personnalisés

et les personnalisés (Voir figure2.1)

ASIC

PERSONNALISES

SEMI-PERSONNALISES

Circuits pré

caractérisés

Circuits à

la demande

Réseaux pré diffusés

Logiques programmables

FPGA

UFigure2.1 : Hiérarchie des circuits

ASIC

2.2.1 ULes circuits semi personnalisés

Les semi personnalisés sont des réseaux

prédéfinis de transistors ou de fonctions logiques qui

nécessitent une personnalisation de l'utilisateur pour réaliser

la fonction désirée. Cette famille comprend :

· · les réseaux logiques programmables,

· · les réseaux

prédiffusés.

2.2.1.1 ULes réseaux

logiques programmablesU

Ce composant ne nécessite aucune étape

technologique supplémentaire pour être personnalisé. Nous y

trouvons les PAL/PLD, ce sont des circuits standard programmables par

l'utilisateur grâce à différents outils de

développement. La programmation consiste à établir des

connexions en imposant un courant supérieur aux courants de

fonctionnement normaux (claquage de fusibles ou de jonctions). Les circuits

logiques programmables incluent un grand nombre de solutions, toutes

basées sur des variantes de l'architecture des portes ET OU.

Nous y trouvons : ·

· PAL (Programmable Array Logic) matrice ET

programmable, matrice OU figée),

· PLA (Programmable Logic Array) matrice ET ou

matrice OU programmable,

· EPLD (Erasable PLD) effaçables par rayons

ultraviolet, ils peuvent être reprogrammer,

· EEPLD (Electrically Erasable PLD) programmables et

effaçables électriquement, ils peuvent être

reprogrammés sur site. Les limites de l'architecture du PLD

résident dans le nombre de bascules, le nombre de signaux

d'entrées/sorties, la rigidité du plan logique ET OU et des

interconnexions.

Précisons que ces composants très souples

d'emploi sont limités à des fonctions numériques et

adaptés à des productions de petites séries et ne

présentent aucune garantie quant à la confidentialité.

2.2.1.2 ULes prédiffusés

U

Les réseaux pré diffusés sont des

circuits partiellement préfabriqués. L'ensemble des

éléments (transistors, diodes, résistances,

capacités, etc.) est déjà implanté sur le circuit

suivant une certaine topologie, mais les éléments ne sont pas

connectés entre eux. La réalisation des connexions dans le but de

définir la fonction souhaitée est la tâche du concepteur,

pour cela il dispose de bibliothèques de macro cellules et d'outils

logiciels d'aide à la conception. A partir de cette liste

d'interconnexions (netlist) le fondeur n'aura que quelques étapes

technologiques à effectuer pour achever le circuit, c'est à dire

le dépôt d'une ou plusieurs couches de métallisation.

Cette technique est intéressante sur le plan de la

conception et de la fabrication, par contre elle présente

l'inconvénient de ne pas permettre une optimisation en terme de

densité de composants puisque les éléments de base sont

pré implantés et pas forcément utilisés et que leur

positionnement a priori n'est pas forcément optimal pour le but

recherché.

2.2.2 ULes circuits

personnalisésU

Ce sont des circuits non préfabriqués. Pour

chaque application on optimise le circuit intégré, ce qui conduit

à la création de son propre composant. Cette famille comprend :

· les circuits à la demande,

· les circuits pré

caractérisés.

2.2.2.1 ULes circuits à la demande

Les solutions circuit à la demande (qu'on appelle full

custom en anglais) présentent l'avantage d'autoriser une meilleure

optimisation du placement puisque celui-ci n'est pas prédéfini.

On dispose d'une bibliothèque de modèles mathématiques de

comportement et via un "compilateur de silicium" logiciel très

sophistiqué on peut concevoir toute l'architecture du circuit en faire

une validation logicielle (simulation logique) puis dans une avant

dernière étape en déduire le dessin des divers masques de

fabrication.

Toutes les opérations, de la conception à la

fabrication, sont effectuées de façons spécifiques

adaptées aux exigences de l'utilisation. L'ensemble des critères

techniques est au choix du concepteur, que ce soit la taille du composant, le

nombre de broches, le placement du moindre transistor. C'est l'ASIC le plus

optimisé car aucune contrainte ne lui est imposée. Le placement

des blocs fonctionnels et le routage des interconnexions, même si ces

opérations sont assistées par ordinateur, sont effectués

avec beaucoup plus d'interventions manuelles pour atteindre l'optimisation au

niveau de chaque transistor. Cependant, les phases de mise au point sont

longues et onéreuses, il va de soi que la rentabilisation des

investissements de développement nécessite un fort volume de

production.

2.2.2.2 ULes circuits

précaractérisésU

Pour la réalisation de circuits pré

caractérisés on dispose d'une bibliothèque de circuits

élémentaires que le fondeur sait fabriquer et dont il peut

garantir les caractéristiques et on les associe pour réaliser le

circuit à la demande. Ici encore on utilisera en fabrication des masques

personnalisés pour chacune des couches diffusées et des

métallisations.

Le concept est très semblable de celui des circuits

à la demande. La seule différence réside dans la

réalisation du schéma puisque l'on accède à une

bibliothèque de cellules prédéfinies

générant de très nombreuses fonctions

élémentaires ou élaborées. Cette dernière

constitue un véritable catalogue dans lequel le concepteur se sert pour

constituer son schéma. Il existe trois types de cellules :

· les cellules standards (standard cells)

correspondent à la logique classique,

· les méga cellules (megacells) peuvent

être des blocs du type microprocesseur, périphérique,

· les cellules compilées (compilable cells) dont

les blocs RAM ou ROM. Il est nécessaire de personnaliser

complètement la diffusion, et par conséquent de créer tous

les masques. Cependant un avantage évident en découle : alors

qu'il est impossible avec les pré diffusés d'utiliser à

100% le réseau de cellules ou portes, ce qui se traduit par une perte de

silicium, les pré caractérisés permettent d'exploiter

complètement la surface du circuit.

UAvantages et inconvénients de

l'utilisation d'ASIC U

D'une manière générale l'utilisation d'un

ASIC conduit à de nombreux avantages provenant essentiellement de la

réduction de la taille des systèmes. Il en ressort :

· Réduction du nombre de composants sur le

circuit imprimé. La consommation et l'encombrement s'en trouvent

considérablement réduits. ·

· Le concept ASIC par définition assure une

optimisation maximale du circuit à réaliser. Nous disposons alors

d'un circuit intégré correspondant réellement à nos

propres besoins.

· La personnalisation du circuit donne une

confidentialité au concepteur et une protection industrielle.

· Enfin, ce type de composant augmente la

complexité du circuit, sa vitesse de fonctionnement et sa

fiabilité.

Dans l'approche des circuits pré diffusés et

personnalisés, l'inconvénient majeur réside dans le fait

du passage obligatoire chez le fondeur ce qui implique des frais de

développement élevés du circuit. En général

le fondeur ne souhaite pas intervenir dans la phase de conception ; sa

tâche est de réaliser le composant à partir des masques.

Dans le but de réduire les surcoûts dus aux modifications, il

s'avère nécessaire d'être rigoureux lors de la phase de

développement de telle sorte que le circuit prototype fonctionne

dès les premiers essais : c'est réussi dans environ 60% des cas.

De plus dans de nombreuses applications, l'utilisateur doit concevoir les

programmes de testabilité.

2.3 UFPGA (Field Programmable Gate Arrays) U [9]

2.3.1. UHistoriqueU

L'histoire des puces programmables

connue plusieurs phases :

En 1975, les concepteurs commencent à

remplacer des circuits logiques standards par des circuits programmables. Les

fonctions réalisées sont majoritairement des interfaces et des

transcodages.

Dans le courant des années 1980, la

société Californienne Xilinx invente une nouvelle famille de

puces programmable appelée FPGA.

Figure2.2 : Puce FPGA

Xilinx

Dès 1985 des contrôleurs et des circuits

périphériques complexes commencent à être

implantés autour des microprocesseurs. Ces cartes sont utilisées

de plus en plus pour effectuer du traitement du signal et dans le domaine des

télécoms. De leur côté, les FPGA se

développent.

En 1987, une première standardisation des

langages de descriptions du hardware est créée. Cette

standardisation permet d'étendre le design de circuit aux particuliers.

En effet, avant cette standardisation, les entreprises utilisaient leur propre

code propriétaire. Cela donna naissance à deux langages :

Le

VHDL, IEEE.1076, facile à appréhender mais peu compact,

principalement utilisé en Europe

Et le Verilog, proche du C,

propriétaire jusqu'à son acceptation IEEE.1364 en 1995,

principalement utilisé aux Etats-Unis.

Depuis les années 1995,

la puissance des circuits logiques programmables FPGA permettent d'implanter en

leur sein à la fois le microprocesseur (ou le DSP) et le pré ou

post traitement associé.

Au début du XXIe siècle, le

prix des puces FPGA commence à baisser et devient progressivement

abordable pour le grand public. Parallèlement à cela, la

modernisation des fonderies permet d'atteindre une finesse de gravure de plus

en plus réduite, donc de créer des puces FPGA de plus en plus

puissantes (fréquence en hausse et nombre de portes

accrues).

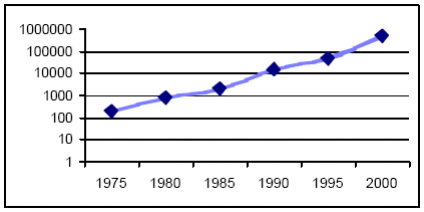

Figure2.3 : Evolution du

nombre de portes

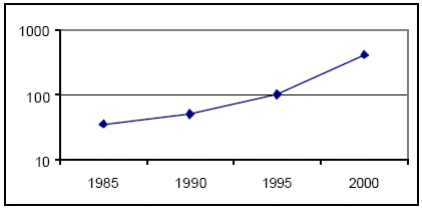

Figure2.4 : Evolution de la

fréquence d'horloge maximum (MHz) d'un compteur synchrone 16

bits

2.3.2. UUtilisation des puces FPGAU

Lors de leur

création vers 1980, les puces FPGA ont tout d'abord su séduire

les électroniciens. Ils y voyaient un moyen de prototypage rapide et peu

cher. En effet, les puces FPGA peuvent êtres reprogrammés sans

nécessiter de matériel lourd. Cela leur permet de tester un

nouveau circuit sans avoir à racheter des composants ou pire de les

reconcevoir à chaque amélioration.

Puis les informaticiens ont

commencé à s'y intéresser de près comme moyen

d'augmenter la rapidité de leur application en leur donnant une assise

matérielle (accélération hardware). Depuis le Geforce 3 de

nVidia (NV20), toutes les cartes graphiques du marché possèdent

un circuit figé et une partie programmable (vertex shader et pixel

shader).

Figure2.5 : vertex shader et pixel

shader

Depuis quelque temps, un certain nombre de chercheurs

intéressé par les principes d'évolution Darwinienne du

hardware utilisent des puces FPGA dans leurs expériences. Elles sont

pour eux intéressantes à plus d'un titre. Elles permettent de

faire évoluer des algorithmes génétiques à des

vitesses électroniques et de concevoir des processeurs

dédiés par ces mêmes

techniques d'algorithmes génétiques.

Les FPGA

ont été perçus par beaucoup comme une alternative à

la fonte même d'un composant : les universités par exemple y

voient un moyen concret d'enseigner le design digital. Les start-up de

l'électronique peuvent à moindre coût prouver que leur

idée est bonne et viable pour lever des fonds sans attendre un retour de

fonderie qui mobilise des capitaux importants, et pour plus d'un mois la

plupart de temps.

La technologie FPGA intéressa aussi l'armée

de par la possibilité de programmation des puces en cours de

fonctionnement. En effet, lors d'une guerre, la réactivité d'un

radar d'avion de chasse par exemple est déterminante pour la survie du

pilote. La possibilité de reprogrammer une puce de type FPGA permet

à ce radar de s'adapter à n'importe quelle situation tout en

ayant une accélération hardware permanente. Globalement,

l'armée est intéressée par des puces FPGA pour les

instruments de vols et les systèmes de communications militaires

nécessitant la possibilité d'être reconfigurés et de

fonctionner dans une large gamme de températures (les deux

dernières puces de marque Altera, EP1S80 et EP1S60, peuvent fonctionner

entre - 40° et 100° C).

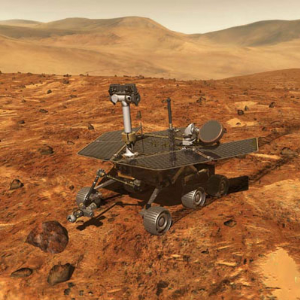

Une puce FPGA de marque Xilinx fut

également choisie par la Nasa pour l'exploration de Mars par les Rovers

Spirit et Opportunity. Ces puces appartiennent à la famille Virtex et

sont spécialement étudiées pour résister aux

radiations solaires qui frappent Mars continuellement (la faible

atmosphère qui entoure Mars ne peut stopper ces radiations et une puce

classique serait détruite en peu de temps). Elle se charge de

contrôler le bras articulé du Rover et les divers appareils de

mesure qui le composent (une accélération hardware permet ici une

plus grande précision). Ce type de puce fut utilisé pour d'autres

missions spatiales tel que Mars orbiter (2005).

Figure2.6 : Rover Spirit sur

Mars

De par leur prix de moins en moins

élevé (une puce à la carte contenant 1 million de portes

s'achète 15 dollars), de plus en plus de personnes voient un moyen de

créer leur propres ordinateurs entièrement personnalisés

à bas prix. Le hardware libre est né vers 2000. Les concepteurs

digitaux en herbe peuvent acheter des puces FPGA puis créer leur propre

design de puce et mettre ce design à disposition d'autres concepteurs. A

l'instar du mouvement logiciel libre, une communauté de concepteurs

passionnés se développe, permettant de s'affranchir des grands

industriels de la micro-électronique.

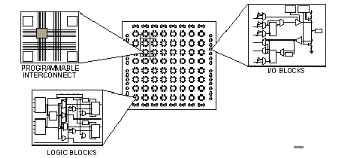

2.3.3 UDescription du FPGAU

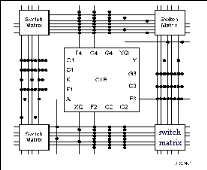

L'architecture, retenue par Xilinx, se présente sous

forme de deux couches :

· une couche appelée circuit configurable,

· une couche réseau mémoire SRAM.

La couche dite 'circuit configurable' est constituée

d'une matrice de blocs logiques configurables CLB permettant de réaliser

des H

TUfonctions

combinatoiresUTH et des H

TUfonctions

séquentiellesUTH. Tout autour de ces blocs logiques

configurables, nous trouvons des blocs entrées/sorties IOB dont le

rôle est de gérer les entrées-sorties réalisant

l'interface avec les modules extérieurs (cf. figure2.7). La

programmation du circuit FPGA appelé aussi LCA (logic cells arrays)

consistera par le biais de l'application d'un potentiel adéquat sur la

grille de certains transistors à effet de champ à interconnecter

les éléments des CLB et des IOB afin de réaliser les

fonctions souhaitées et d'assurer la propagation des signaux. Ces

potentiels sont tout simplement mémorisés dans le réseau

mémoire SRAM.

Figure2.7 :Architecture interne d'un

FPGA.

Les circuits FPGA du fabricant Xilinx utilisent deux types de

cellules de base :

· les cellules d'entrées/sorties appelés

IOB (input output bloc),

· les cellules logiques appelées CLB (configurable

logic bloc). Ces différentes cellules sont reliées entre elles

par un réseau d'interconnexions configurable.

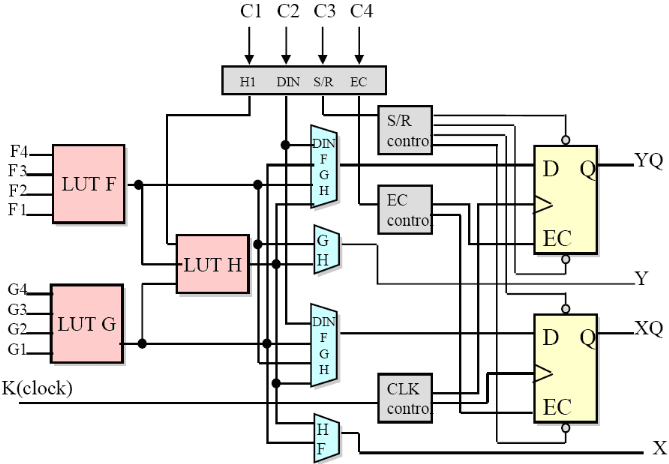

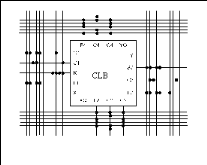

2.3.3.1 Les CLB (configurable logic bloc)

Les blocs logiques configurables sont les éléments

déterminants des performances du FPGA. Chaque bloc est composé

d'un bloc de logique combinatoire composé de deux

générateurs de fonctions à quatre entrées et d'un

bloc de mémorisation synchronisation composé de deux bascules D.

Quatre autres entrées permettent d'effectuer les connexions internes

entre les différents éléments du CLB. La figure

ci-dessous, nous montre le schéma d'un CLB.

Figure2.8: Cellule logique (CLB)

Voyons d'abord le bloc logique combinatoire qui possède

deux générateurs de fonctions F' et G' à quatre

entrées indépendantes (F1...F4, G1...G4), lesquelles offrent aux

concepteurs une flexibilité de développement importante car la

majorité des fonctions aléatoires à concevoir

n'excède pas quatre variables. Les deux fonctions sont

générées à partir d'une table de

vérité câblée inscrite dans une zone mémoire,

rendant ainsi les délais de propagation pour chaque

générateur de fonction indépendants de celle à

réaliser. Une troisième fonction H' est réalisée

à partir des sorties F' et G' et d'une troisième variable

d'entrée H1 sortant d'un bloc composé de quatre signaux de

contrôle H1, Din, S/R, Ec. Les signaux des générateurs de

fonction peuvent sortir du CLB, soit par la sortie X, pour les fonctions F' et

G', soit Y pour les fonctions G' et H'. Ainsi un CLB peut être

utilisé pour réaliser:

· deux fonctions indépendantes à quatre

entrées indépendantes, plus une troisième fonction de

trois variables indépendantes

· ou toute fonction à cinq variables

· ou toute fonction à quatre variables et une

autre avec quelques fonctions à six variables

· ou certaines fonctions jusqu'à neufs

variables.

L'intégration de fonctions à nombreuses

variables diminue le nombre de CLB nécessaires, les délais de

propagation des signaux et par conséquent augmente la densité et

la vitesse du circuit. Les sorties de ces blocs logiques peuvent être

appliquées à des bascules au nombre de deux ou directement

à la sortie du CLB (sorties X et Y). Chaque bascule présente deux

modes de fonctionnement : un mode 'flip-flop' avec comme

donnée à mémoriser, soit l'une des fonctions F', G', H'

soit l'entrée directe DIN et un mode latch. La

donnée peut être mémorisée sur un front

montant ou descendant de l'horloge (CLK). Les sorties de ces deux

bascules correspondent aux sorties du CLB XQ et YQ. Un mode dit de "

verrouillage " exploite une entrée S/R qui peut être

programmée soit en mode SET, mise à 1 de la bascule, soit en

Reset, mise à zéro de la bascule. Ces deux entrées

coexistent avec une autre entrée laquelle n'est pas

représentée sur la figure, appelée le global Set/Reset.

Cette entrée initialise le circuit FPGA à chaque mise sous

tension, à chaque configuration, en commandant toutes les bascules au

même instant soit à '1', soit à '0'. Elle agit

également lors d'un niveau actif sur le fil RESET lequel peut être

connecté à n'importe quelle entrée du circuit FPGA.

Un mode optionnel des CLB est la configuration en

mémoire RAM de 16x2bits ou 32x1bit ou 16x1bit. Les entrées F1

à F4 et G1 à G4 deviennent des lignes d'adresses

sélectionnant une cellule mémoire particulière. La

fonctionnalité des signaux de contrôle est modifiée dans

cette configuration, les lignes H1, DIN et S/R deviennent respectivement les

deux données D0, D1 (RAM 16x2bits) d'entrée et le signal de

validation d'écriture WE. Le contenu de la cellule mémoire (D0 et

D1) est accessible aux sorties des générateurs de fonctions F' et

G'. Ces données peuvent sortir du CLB à travers ses sorties X et

Y ou alors en passant par les deux bascules.

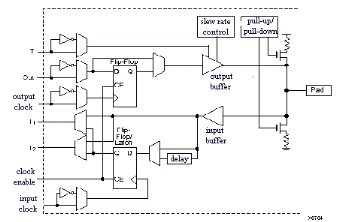

2.3.3.2 Les IOB (input output bloc)

La figure ci-dessous présente la structure de ce bloc. Ces

blocs entrée/sortie permettent l'interface entre les broches du

composant FPGA et la logique interne développée à

l'intérieur du composant. Ils sont présents sur toute la

périphérie du circuit FPGA. Chaque bloc IOB contrôle une

broche du composant et il peut être défini en entrée, en

sortie, en signaux bidirectionnels ou être inutilisé (haute

impédance).

Figure2.9 : Input Output Block

(IOB).

2.3.3.2.1Configuration en

entrée

Premièrement, le signal d'entrée

traverse un buffer qui selon sa programmation peut détecter soit des

seuils TTL ou soit des seuils CMOS. Il peut être routé directement

sur une entrée directe de la logique du circuit FPGA ou sur une

entrée synchronisée. Cette synchronisation est

réalisée à l'aide d'une bascule de type D, le changement

d'état peut se faire sur un front montant ou descendant. De plus, cette

entrée peut être retardée de quelques nanosecondes pour

compenser le retard pris par le signal d'horloge lors de son passage par

l'amplificateur. Le choix de la configuration de l'entrée s'effectue

grâce à un multiplexeur (program controlled multiplexer). Un bit

positionné dans une case mémoire commande ce dernier.

2.3.3.2.2 Configuration en sortie

Nous distinguons les possibilités suivantes :

· inversion ou non du signal avant son application

à l'IOB,

· synchronisation du signal sur des fronts montants ou

descendants d'horloge,

· mise en place d'un " pull-up " ou " pull-down " dans le

but de limiter la consommation des entrées sorties inutilisées,

· signaux en logique trois états ou deux

états. Le contrôle de mise en haute impédance et la

réalisation des lignes bidirectionnelles sont commandés par le

signal de commande Out Enable lequel peut être inversé ou non.

Chaque sortie peut délivrer un courant de 12mA. Ainsi toutes ces

possibilités permettent au concepteur de connecter au mieux une

architecture avec les périphériques extérieurs.

2.3.3.3 Les différents types

d'interconnexions [8]

Les connexions internes dans les circuits FPGA sont

composées de segments métallisés. Parallèlement

à ces lignes, nous trouvons des matrices programmables réparties

sur la totalité du circuit, horizontalement et verticalement entre les

divers CLB. Elles permettent les connexions entre les diverses lignes,

celles-ci sont assurées par des transistors MOS dont l'état est

contrôlé par des cellules de mémoire vive ou RAM. Le

rôle de ces interconnexions est de relier avec un maximum

d'efficacité les blocs logiques et les entrées/sorties afin que

le taux d'utilisation dans un circuit donné soit le plus

élevé possible. Pour parvenir à cet objectif, Xilinx

propose trois sortes d'interconnexions selon la longueur et la destination des

liaisons. Nous disposons :

· d'interconnexions à usage général,

· d'interconnexions directes,

· de longues lignes.

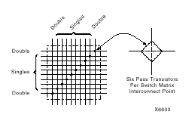

2.3.3.3.1 Les interconnexions à usage

général

Ce système fonctionne en une grille de cinq segments

métalliques verticaux et quatre segments horizontaux positionnés

entre les rangées et les colonnes de CLB et de l'IOB.

Figure2.10 : Connexions à usage

général et détail d'une matrice de

commutation

Des aiguilleurs appelés aussi matrices de commutation

sont situés à chaque intersection. Leur rôle est de

raccorder les segments entre eux selon diverses configurations, ils assurent

ainsi la communication des signaux d'une voie sur l'autre. Ces interconnexions

sont utilisées pour relier un CLB à n'importe quel autre. Pour

éviter que les signaux traversant les grandes lignes ne soient

affaiblis, nous trouvons généralement des buffers

implantés en haut et à droite de chaque matrice de commutation.

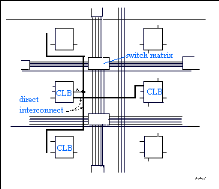

2.3.3.3.2 Les interconnexions directes

[8]

Ces interconnexions permettent l'établissement de

liaisons entre les CLB et les IOB avec un maximum d'efficacité en terme

de vitesse et d'occupation du circuit. De plus, il est possible de connecter

directement certaines entrées d'un CLB aux sorties d'un autre.

Figure2.11 : Les interconnexions

directes

Pour chaque bloc logique configurable, la sortie X peut

être connectée directement aux entrées C ou D du CLB

situé au-dessus et les entrées A ou B du CLB situé

au-dessous. Quant à la sortie Y, elle peut être connectée

à l'entrée B du CLB placé immédiatement à sa

droite. Pour chaque bloc logique adjacent à un bloc

entrée/sortie, les connexions sont possibles avec les entrées I

ou les sorties O suivant leur position sur le circuit.

2.3.3.3.3 Les longues lignes

Les longues lignes sont de longs segments

métallisés parcourant toute la longueur et la largeur du

composant, elles permettent éventuellement de transmettre avec un

minimum de retard les signaux entre les différents

éléments dans le but d'assurer un synchronisme aussi parfait que

possible. De plus, ces longues lignes permettent d'éviter la

multiplicité des points d'interconnexion.

Figure2.12 : Les longues

lignes

2.3.3.3.4 Performances des interconnexions

Les performances des interconnexions dépendent du type

de connexions utilisées. Pour les interconnexions à usage

général, les délais générés

dépendent du nombre de segments et de la quantité d'aiguilleurs

employés. Le délai de propagation de signaux utilisant les

connexions directes est minimum pour une connectique de bloc à bloc.

Quant aux segments utilisés pour les longues lignes, ils

possèdent une faible résistance mais une capacité

importante. De plus, si on utilise un aiguilleur, sa résistance s'ajoute

à celle existante.

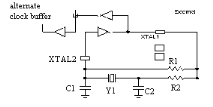

2.3.3.4 L'oscillateur à quartz

Placé dans un angle de la puce, il peut être

activé lors de la phase de programmation pour réaliser un

oscillateur. Il utilise deux IOB voisins, pour réaliser l'oscillateur

dont le schéma est présenté ci-dessous. Cet oscillateur ne

peut être réalisé que dans un angle de la puce où se

trouve l'amplificateur prévu à cet effet. Il est évident

que si l'oscillateur n'est pas utilisé, les deux IOB sont utilisables au

même titre que les autres IOB.

Figure2.13 : L'oscillateur à

quartz

2.3.4 ULes

caractéristiquesU [7]

Le tableau présenté ci-dessous désigne la

quantité de ressources disponible pour les différents composants

de la série 4000E proposée par le fabricant Xilinx.

|

Device

|

Logic cells

|

Max logic

Gates

(No RAM)

|

Max RAM

Bits

(No logic)

|

Typical

Gate Range

(Logic and RAM)

|

CLB

Matrix

|

Total

CLBs

|

Number

Of

Flip-Flops

|

Max.

User I/O

|

|

XC4003E

|

238

|

3,000

|

3,200

|

2,000- 5,000

|

10×10

|

100

|

360

|

80

|

|

XC4005E/XL

|

466

|

5,000

|

6,272

|

3,000-9,000

|

14×14

|

196

|

616

|

112

|

|

XC4006E

|

608

|

6,000

|

8,192

|

4,000-12,000

|

16×16

|

256

|

768

|

128

|

|

XC4008E

|

770

|

8,000

|

10,368

|

6,000-15,000

|

18×18

|

324

|

936

|

144

|

|

XC4010E/XL

|

950

|

10,000

|

12,800

|

7,000-20,000

|

20×20

|

400

|

1,120

|

160

|

|

XC4013/XL

|

1368

|

13,000

|

18,432

|

10,000-30,000

|

24×24

|

578

|

1,536

|

192

|

|

XC4020E/XL

|

1862

|

20,000

|

25,088

|

13,000-40,000

|

28×28

|

784

|

2,016

|

224

|

|

XC4025E

|

2432

|

25,000

|

32,768

|

15,000-45,000

|

32×32

|

1,024

|

2,560

|

256

|

|

XC4028EX/XL

|

2432

|

28,000

|

32,768

|

18,000-50,000

|

32×32

|

1,024

|

2,560

|

256

|

|

XC4036EX/XL

|

3078

|

36,000

|

41,472

|

22,000-65,000

|

36×36

|

1,296

|

4,576

|

352

|

|

XC4044XL

|

3800

|

44,000

|

51,200

|

27,000-80,000

|

40×40

|

1,600

|

3,840

|

320

|

|

XC4052XL

|

4598

|

52,000

|

61,952

|

33,000-100,000

|

44×44

|

1,936

|

4,576

|

352

|

|

XC4062XL

|

5472

|

62,000

|

73,728

|

40,000-130,000

|

48×48

|

2,304

|

5,376

|

384

|

|

XC4085XL

|

7448

|

85,000

|

100,352

|

55,000-180,000

|

56×56

|

3,136

|

7,168

|

448

|

UTableau2.1 : URessources de

la série 4000EU

Ces composants sont disponibles dans tous types de

boîtiers adaptés au nombre de sorties et à la technologie

utilisée pour le montage des circuits FPGA sur des cartes

électroniques. Nous pouvons utiliser des boîtiers de type PGA,

PLCC et PQFP.

2.3.5 Technique de programmation des FPGA [7]

Les circuits FPGA ne possèdent pas de programme

résident. A chaque mise sous tension, il est nécessaire de les

configurer. Leur configuration permet d'établir des interconnexions

entre les CLB et IOB. Pour cela, ils disposent d'une RAM interne dans laquelle

sera écrit le fichier de configuration. Le format des données du

fichier de configuration est produit automatiquement par le logiciel de

développement sous forme d'un ensemble de bits organisés en

champs de données. Le FPGA dispose de quatre modes de chargement et de

trois broches M0, M1, M2 lesquelles définissent les différents

modes. Ces modes définissent les différentes méthodes pour

envoyer le fichier de configuration vers le circuit FPGA, selon deux approches

complémentaires :

· configuration automatique, le circuit FPGA est

autonome,

· configuration externe, l'intervention d'un

opérateur est nécessaire.

· M0 M1 M2 Mode sélectionné

o 0 0 0 maître série

o 0 0 1 maître parallèle bas

o 0 1 1 maître parallèle haut

o 1 0 1 périphérique

o 1 1 1 esclave série

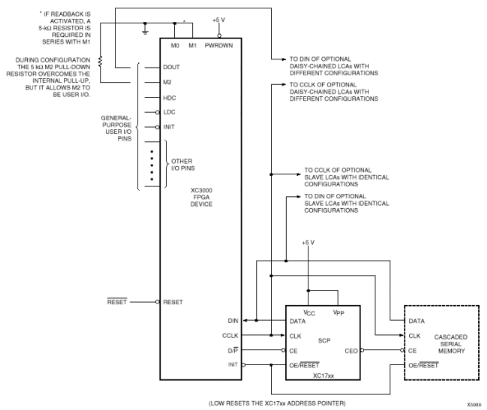

2.3.5.1 Mode maître série

Le mode maître série utilise une mémoire

à accès série de type registre à décalage

commercialisée par le fabricant Xilinx. Le programme est

préalablement chargé par le système de

développement utilisé pour le circuit FPGA. Le FPGA

génère tous les signaux de dialogue nécessaires pour la

copie du contenu de la PROM dans sa RAM interne, lorsque la copie est

terminée, il bascule le signal DONE pour le signaler au circuit. Comme

nous pouvons le remarquer sur la figure, une seule PROM peut configurer

plusieurs circuits FPGA avec la même configuration ou plusieurs PROM

peuvent configurer plusieurs FPGA en chaîne où le premier des

circuits FPGA est le maître et génère l'horloge. Les

données en provenance des PROM sont envoyées aux autres circuits

FPGA par la sortie DOUT de ce premier

Figure2.14 : Mode maître

série

Figure2.15 : Schémas de programmation en

mode maître série

On dispose aussi d'un mode maître-parallèle

où le FPGA est relié en parallèle à une EPROM

classique, de même qu'un mode passif type périphérique dans

lequel le FPGA est considéré comme un périphérique

de uP et peut-être configuré à partir de celui-ci

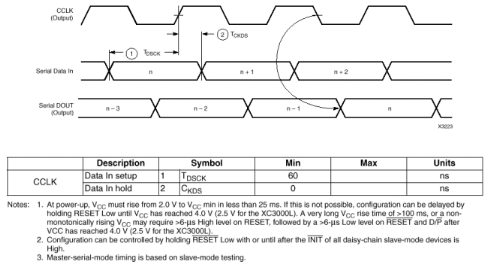

2.3.5.2 Mode esclave

Dans ce mode, le programme de configuration peut être

envoyé à partir d'un PC, d'une station de travail ou à

partir d'un autre circuit FPGA. Le circuit FPGA maître peut être

interfacé à une mémoire en mode parallèle ou

série sans apporter aucune modification au niveau du câblage des

circuits FPGA esclaves. C'est souvent le mode exploité pour la mise au

point d'une configuration.

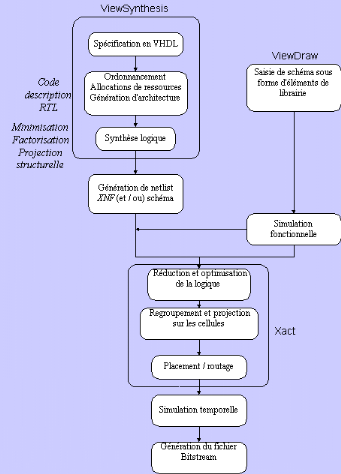

2.3.6 Les outils de développement des FPGA

[7]

Xilinx a développé des logiciels de

développement performants capables de fonctionner sur des stations de

travail telles que Sun, Appolo, Dec et sur des PC AT disposant d'une

mémoire suffisante. La programmation des circuits FPGA est

réalisée à l'aide des logiciels Viewlogic (Workview Office

7.31) et Xact (Design Manager 6.01). Elle est décomposée en

plusieurs étapes :

· la synthèse logique,

· la simulation fonctionnelle,

· l'optimisation, la projection et le placement /

routage,

· la simulation temporelle,

· la génération de fichier de

configuration.

2.3.6.1 La synthèse logique

La synthèse logique peut s'effectuer de diverses

manières avec différentes interfaces afin de

générer le circuit électrique, parmi lesquelles nous

pouvons citer :

· une entrée de type équations logiques de

" haut niveau ", de table de vérité et de machine d'état

avec une interface comme ABEL,

· une entrée de type schématique " bas

niveau " avec une interface comme ViewDraw,

· une entrée de type textuelle " haut niveau "

avec le VHDL à l'aide d'une interface comme ViewSynthesis, Synopsis,

Alliance et ISE ou le HDL de Verilog à l'aide d'une interface comme

Cadence Opus.

Nous allons voir en détail la synthèse logique

avec une entrée schématique et une entrée en VHDL.

2.3.6.1.1 Saisie de schéma

A l'aide de l'interface ViewDraw, la réalisation de

circuits se fait à base de cellules standards (portes logiques

pré caractérisées). On décrit la structure d'un

circuit à l'aide de connexions sur des cellules de base à partir

d'une librairie. Il existe deux types de cellules dans la librairie Xilinx :

· les soft-macros qui sont implantées en fonction

des flips-flops et des générateurs de fonctions disponibles,

· les hard-macros qui sont préroutées et

utilisent complètement les CLB qu'elles occupent.

La saisie de schéma à partir de cellules de base

permet un développement " bas niveau " qui rend difficile la

réalisation de circuits complexes où chaque changement ou

amélioration remet en cause toute la description. Cette contrainte a

conduit à étudier des techniques de génération de

circuits à partir de spécifications de " haut niveau " tel que le

VHDL (VHSIC Hardware Description Language avec VHSIC : Very High Speed

Integrated Circuits) qui se traduit en français par : langage de

description de matériel traitant des circuits intégrés

à très grande vitesse.

2.3.6.1.2 La synthèse en VHDL

La méthodologie [XILI98] [VIEW94] de la synthèse

en VHDL se compose de trois étapes :

· spécification en VHDL,

· synthèse du code VHDL,

· implantation physique.

2.3.6.1.2.1 Spécification en

VHDL

Le langage VHDL est un langage de description de

matériel qui permet de synthétiser des fonctions logiques

complexes. A l'aide de ce langage, la première description

définit la fonctionnalité du circuit en terme de blocs

définis " haut niveau ". Progressivement, les blocs sont

détaillés précisément jusqu'à une

description proche des ressources matérielles. En effet, le langage VHDL

autorise trois niveaux de description :

· le niveau structurel décrit le câblage des

composants élémentaires,

· le niveau flot de données décrit les

transformations d'un flot de données de l'entrée à la

sortie,

· le niveau comportemental décrit le

fonctionnement par des blocs programmes appelés Processus qui

échangent des données au moyen de signaux comprenant des

instructions séquentielles.

2.3.6.1.2.2 Synthèse du code

VHDL

La synthèse permet à partir d'une

spécification VHDL, la génération d'une architecture au

niveau transfert de registre RTL (register transfert level) qui permet

l'ordonnancement et l'allocation de ressources sans une représentation

physique, compilable par un outil de synthèse logique. Cette

étape est réalisable à condition de se limiter à un

sous ensemble du langage VHDL qui soit strictement synthétisable.

2.3.6.1.2.3 Implantation physique

La spécification VHDL est directement

émulée sur un support matériel tel qu'un circuit FPGA en

précisant la famille utilisée pour une implantation physique du

circuit. La compilation du code VHDL en code FPGA permet de

générer le schéma correspondant et une netlist (XNF)

constituée d'une liste d'équations booléennes et

d'informations portant sur les entrées / sorties du circuit. L'outil de

synthèse ViewSynthesis ne permet pas de faire une simulation

comportementale à partir du code VHDL, par conséquent il faut

réaliser ces trois étapes à tous les niveaux de conception

avant de faire une simulation fonctionnelle.

2.3.6.2 Simulation fonctionnelle

ViewSim est une interface qui, à partir de vecteurs

d'entrée (reset, clk...etc.) appliqués sur certains noeuds du

schéma et à partir d'une modélisation des composants, va

générer sur chaque noeud du schéma des signaux

représentant le fonctionnement réel du circuit. Nous pouvons

visualiser la forme des signaux à l'aide de l'interface ViewTrace. La

simulation fonctionnelle ne tient pas compte des capacités de liaison

dues au routage entre les différentes cellules. Elle permet donc de

vérifier uniquement la validité du circuit par rapport au cahier

des charges d'un point de vue fonctionnel et non d'un point de vue temporel.

2.3.6.3 Optimisation, projection et placement /

routage

2.3.6.3.1 Optimisation

Avant l'utilisation de la netlist, celle-ci est

optimisée. Cette étape gère les problèmes de

sortance des signaux par la duplication des fonctions logiques de sortance

insuffisante, afin de multiplier les sortances. Les signaux inutilisés

sont retirés, les expressions booléennes sont simplifiées,

les signaux équivalents sont détectés.

2.3.6.3.2 Projection

La phase de projection dépend du circuit

utilisé, les équations de la netlist sont transformées,

regroupées en de nouvelles équations ayant un nombre d'arguments

inférieur ou égal au nombre de paramètres du bloc logique

correspondant à la famille de circuit utilisée.

2.3.6.3.3 Placement / routage

L'étape suivante consiste à attribuer les

cellules (CLB) du circuit à chaque équation

délivrée par la projection et à définir les

connexions. L'algorithme de placement place physiquement les différentes

cellules et les chemins d'interconnexion dessinés entre les cellules

afin de faciliter le routage. Des directives jointes à la netlist

permettent une bonne répartition des cellules. Ces trois

opérations sont réalisées par le logiciel Xact (Designer

Manager).

2.3.6.4 Simulation temporelle

Il s'agit de vérifier la fonctionnalité du

circuit en prenant en compte par un calcul estimatif les longueurs

d'interconnexion et les retards apportés par les capacités

parasites liées au partionnement et au routage. La simulation temporelle

vérifie que la fonctionnalité n'a pas été

modifiée par l'introduction des délais de propagation et reste

conforme au cahier des charges.

2.3.6.5 Génération du fichier de

configuration

La dernière étape consiste à

générer un fichier de configuration appelé Bitstream dans

une PROM. Ce fichier contient les informations fournies au composant FPGA

Xilinx afin qu'il prenne la configuration souhaitée. Ci-dessous,

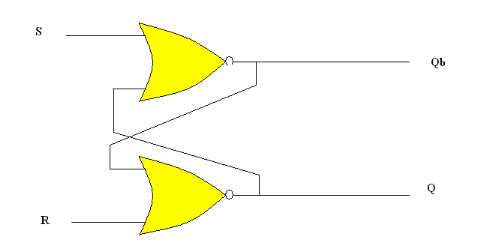

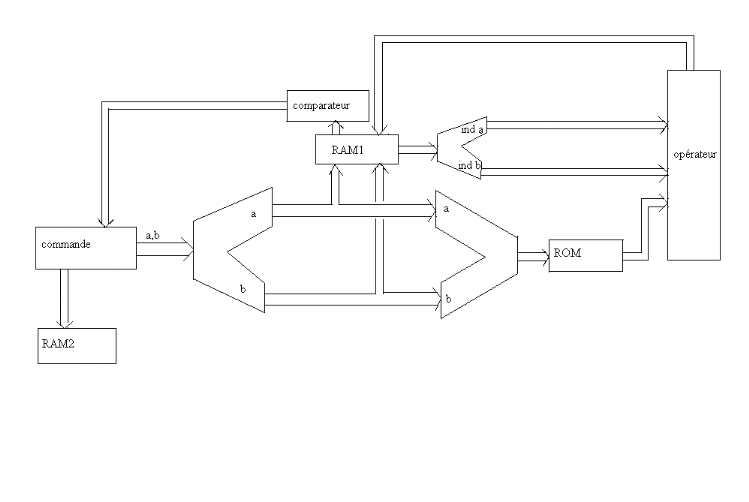

l'organigramme représentant la procédure de programmation des

circuits FPGA :

Figure2.16 : Programmation des composants FPGA

[7]

Conclusion

Dans ce chapitre, nous avons présenté les

circuits de type FPGA dont nous précisons ici les principaux avantages :

· Le premier argument est la souplesse de programmation

qui permet l'emploi conjoint d'outils de schématique aussi bien que

l'exploitation d'un langage de haut niveau tel VHDL. Ce qui permet de

multiplier les essais, d'optimiser de diverses manières l'architecture

développée, de vérifier à divers niveaux de

simulation la fonctionnalité de cette architecture.

· Le second argument est évidemment la nouvelle

possibilité de reconfiguration dynamique partielle ou totale d'un

circuit ce qui permet d'une part, une meilleure exploitation du composant, une

réduction de surface de silicium employé et donc du coût,

et d'autre part, une évolutivité assurant la possibilité

de couvrir à terme des besoins nouveaux sans nécessairement

repenser l'architecture dans sa totalité. L'un des points forts de la

reconfiguration dynamique est effectivement de permettre de reconfigurer en

temps réel en quelques microsecondes tout ou partie du circuit, c'est

à dire de permettre de modifier la fonctionnalité d'un circuit en

temps quasi réel. Ainsi le même CLB pourra à un instant

donné être intégré dans un processus de filtrage

numérique d'un signal et l'instant d'après être

utilisé pour gérer une alarme. On dispose donc quasiment de la

souplesse d'un système informatique qui peut exploiter successivement

des programmes différents, mais avec la différence fondamentale

qu'ici il ne s'agit pas de logiciel mais de configuration matérielle, ce

qui est infiniment plus puissant.

· Notons enfin que ces circuits n'ont pas vocation

à concurrencer les super calculateurs, mais plutôt à offrir

une alternative en fonction de critères comme l'encombrement, les

performances et le prix, et sont de ce fait bien adaptés à des

applications de qualité dans le domaine des systèmes ambulatoires

ou nomades.

· Enfin il semble que de plus en plus fréquemment

les concepteurs de circuits ASIC préfèrent passer par

l'étape intermédiaire d'un FPGA ce qui est moins risqué

économiquement, puis une fois que le modèle FPGA est au point, il

est alors relativement aisé de le retranscrire dans une architecture de

type prédiffusé ou précaractérisés. Ce que

tous les fondeurs de silicium savent effectivement faire pour en faire un

circuit réellement personnalisé et confidentiel. Le FPGA

n'étant évidemment pas un circuit très

sécurisé sur le plan de la confidentialité puisqu'il

suffit d'analyser le contenu de la ROM associée pour remonter à

la schématique imaginée.

CHAPITRE 3 : LE LANGAGE VHDL ET LA CONCEPTION DE

CIRCUITS

3.1 UIntroductionU